Компютерна схемотехніка 2

СОДЕРЖАНИЕ: МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ ЧЕРНІВЕЦЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ ІМЕНІ ЮРІЯ ФЕДЬКОВИЧА Факультет комп’ютерних наук Кафедра комп’ютерних систем та мережМІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

ЧЕРНІВЕЦЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ

ІМЕНІ ЮРІЯ ФЕДЬКОВИЧА

Факультет комп’ютерних наук

Кафедра комп’ютерних систем та мереж

Курсова робота

Комп’ютерна схемотехніка

2007

1. Лінійні дешифратори. Функції алгебри логіки, таблиці істинності та структурна схема. Оцінка їх складності та швидкодії. Каскадування дешифраторів

Дешифратори – це комбінаційні вузли призначені для перетворення n-розрядного позиційного коду в унітарний код.

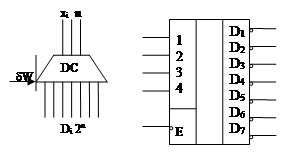

Функціональне позначення дешифраторів:

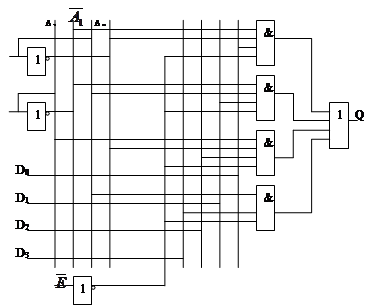

Позначення на схемі К155ND7.

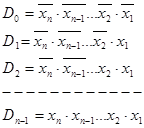

Логіка роботи дешифратора може бути описана наступним співвідношенням, що визначає зв’язок між вхідними сигналами і вихідними сигналами пристрою.

Для дешифратора 38 таблиця істинності має наступний вигляд (з інверсними виходами):

| x3 |

x2 |

x1 |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

| 0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

| 0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

| - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - |

||||||||||

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

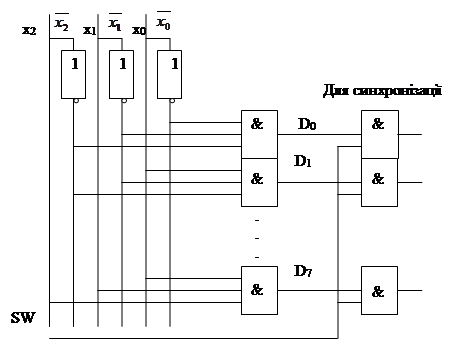

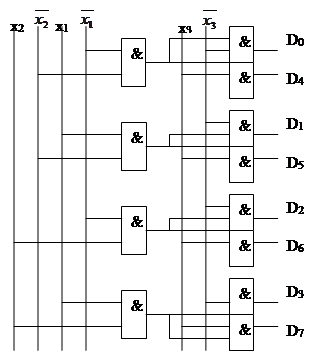

В найпростішому випадку таку схему можна реалізувати з допомогою тривходових кон’юнкторів.

Складність такого пристрою, побудованого за лінійною схемою, визначається кількістю елементів, що формують вихідні сигнали і визначається: L = 2n .

Вартість за Квайном: K = n2n .

Час затримки визначається часом проходження каскаду: t = tз .

Окрім лінійних схем за структурною будовою розрізняють ще каскади і пірамідальні дешифратори.

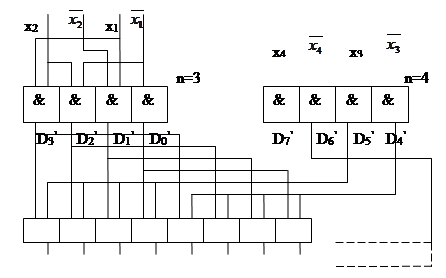

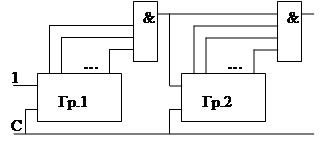

При каскадній побудові дешифратор використовує методику розбиття дешифрованого слова на кілька підслів. При цьому в окремому каскаді проводиться дешифрації одного підслова, в наступному каскаді дешифруються слова з допомогою кон’юнкції вихідних сигналів дешифратора до повного слова.

В загальному в каскадних дешифраторах кількість входів на окремих дешифраторах підслів є меншою, але число схем, що забезпечують те саме перетворення, залишається тим самим або дещо зростає.

В таблиці істинності для каскадних дешифраторів виділяють блоки за певним значенням вхідних змінних. Структурна схема такого дешифратора розділяється на вхідний та наступні до вхідного каскади.

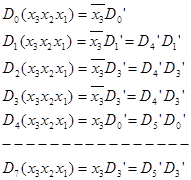

Функції логічних виходів в цьому випадку записуються як лінійна комбінація дешифрованих підслів. Для n=3 можемо записати:

Каскадні схеми зручно використовувати для дешифрації логічних функцій багатьох змінних, якщо їх потрібно реалізовувати з допомогою елементів з малою кількістю реальних фізичних кодів.

В загальному випадку при проектуванні каскадних дешифраторів на базі логічних елементів з показником Мn (показник об’єднання за входом, n – кількість змінних) основним завданням є забезпечити максимальні швидкодії пристроїв при мінімальній складності схеми. Тоді всі змінні, тобто кодове слово з n розрядів, розбиваються на підслова по ![]() розрядів,

розрядів, ![]() - розрядність підслова, m – число розрядів підслова.

- розрядність підслова, m – число розрядів підслова.

Швидкодія оптимізаційного пристрою оцінюється співвідношенням:

![]()

Складність схеми описується числовим рядом:

![]()

![]() , ni

– розрядність кодових підслів. Мінімальна складність одержується тоді, коли

, ni

– розрядність кодових підслів. Мінімальна складність одержується тоді, коли

![]() .

.

В пірамідальних дешифраторах схемотехнічною особливістю є те, що кожна конституанта одиниці в певному каскаді формується за допомогою дешифрованого підслова з певної кількості вхідних розрядів і додаткового сигналу, тобто змінної, яка ще не була задіяна в дешифрації.

Час затримки:

![]()

Складність схеми:

![]()

Наприклад, для функції трьох змінних пірамідальний дешифратор можна реалізувати за наступною схемою.

Недоліком пірамідальних дешифраторів є ускладнення топології схеми при зростанні їх розрядності, тому більшого застосування набули дешифратори, які будуються за каскадною та лінійною схемою.

Для реалізації комбінаційних схем використовують регулярні структури, в яких окрім вхідних сигналів змінних Аі та вихідних дешифрованих сигналів застосовують керуючі сигнали Вr для каскадного нарощування регулярних структур.

Різновидністю дешифраторів є схеми, які використовуються для керування індикаторними пристроями.

2. Мультиплексори і демультиплексори. Їх призначення, функції алгебри логіки, таблиці істинності та синтез структурних схем. Каскадування мультиплексорів і демультиплексорів

Мультиплексори – пристрої, призначені для комутації кількох інформаційних сигналів на один інформаційний канал. В загальному випадку можна комутувати кілька груп сигналів на одну інформаційну шину. Розрізняють мультиплексори цифрових та аналогових сигналів.

В І випадку комбінаційна схема, що забезпечує мультиплексування, може довільним чином трансформувати набір вхідних сигналів, але повинна забезпечуватись тільки відповідність вихідного сигналу до одного з інформаційних сигналів, що подаються на вхід пристрою.

При мультиплексуванні аналогових сигналів комбінаційні схеми використовуються тільки для комутації відповідних аналогових ключів, під’єднаних до заданого інформаційного входу.

В інтегральних схемах мультиплексора розрізняють вхідні інформаційні сигнали, сигнали керування та сигнали адресації.

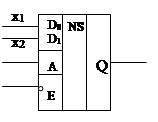

При реалізації комбінаційної схеми доцільно розділити адресні та інформаційні коди, згрупувавши їх у дві шини.

| E |

D0 |

D1 |

A |

Q |

| 0 |

0 |

1 |

0 |

D0 |

| 0 |

0 |

1 |

1 |

D1 |

| 1 |

0 |

1 |

0 |

|

| 1 |

0 |

1 |

1 |

Активація інформаційних сигналів забезпечується за допомогою двовходових диз’юнкторів.

Демультиплексори призначені для комутації одного інформаційного сигналу на кілька входів. Умовне позначення мультиплексора:

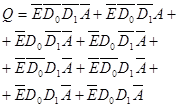

Логічні функції, які описують вихідні стани мультиплексора, враховують як інформаційні, так і адресний сигнали, а також сигнал керування.

Комбінаційна схема для мультиплексора дещо простіша, оскільки вхідний сигнал лише один.

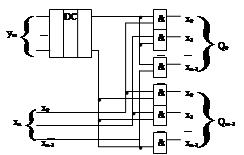

Багаторозрядні комутатори сигналів розробляють на основі уніфікованих інтегральних схем з меншою розрядністю, використовуючи каскадування. Головний принцип стосується вибору адресації молодших і старших сигналів, який забезпечується від першого вхідного до другого вихідного каскаду.

Мультиплексор 161 може бути побудований на основі чотирьох входових елементів. Така структура ще має назву мультиплексного дерева. Сигнал синхронізації Е об’єднується для всіх вузлів одночасно.

Аналогічним чином будується демультиплексне дерево, тоді кількість інтегральних вузлів буде зростати від першого до останнього каскаду. Схема такого демультиплексора 116 має вигляд:

Для комутації цілих шин можна використовувати демультиплексори побудовані на основі дешифраторів.

В якості комутуючих елементів вихідного каскаду в цифрових схемах можна застосовувати логічні кон’юнктори. Узагальнена схема такого демультиплексора включає багатоканальний вхід сигналів хn , шину керування y і вихідні ключі, згруповані по n елементів.

3. Перетворювачі кодів. Функціональний опис, таблиці істинності та структурні схеми перетворювачів прямого коду в обернений та додатковий

За функціональним значенням комбінаційні схеми перетворювачів кодів є найбільш розповсюдженими. В першу чергу це схеми перетворення двійкових чисел в обернений чи доповнюючий код, схеми переходу із однієї системи числення в іншу, схеми шифрування і дешифрування.

Перетворювачі прямого коду в зворотній повинні отримувати додатковий розряд знаку числа, тобто, маючи n-1 вхід, вони повинні мати n виходів.

Таблиці істинності для однобітного перетворювача описуються функцією виключного АБО:

| x0 |

x1 |

fi (x0 ,x1 ) |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Функція алгебри логіки буде мати вигляд:

![]()

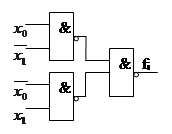

Для реалізації в базисі І-НЕ необхідно провести подвійну інверсію:

![]()

Багаторозрядні перетворювачі можна релізувати у вигляді регулярної структури на основі вказаних комірок, при цьому знаковий біт повинен комутуватися з усіма елементарними комірками. Таку інтегральну схему використовують, як вбудовану в інші структури.

Для перетворення прямого коду в доповнюючий, крім інверсії числа - чи збереження + в останні біти потрібно провести сумування 1.

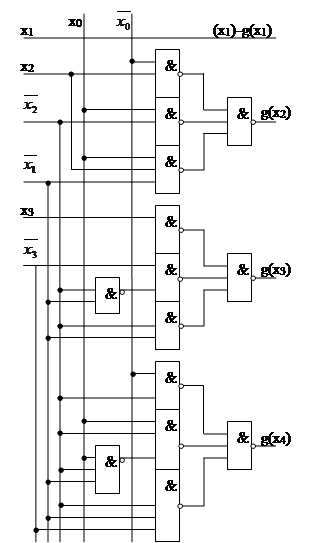

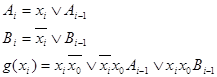

В загальному випадку функціональна залежність для і-того біта описується співвідношенням:

Враховуючи правила де Моргана, можна записати:

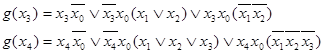

Для n=4 відповідні функції матимуть вигляд:

![]()

![]()

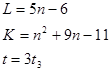

Для такої схеми при довільній розрядності n складність визначається:

Недоліком такої схеми є необхідність використовувати кон’юнктивні елементи з різною кількістю лінійних входів. Причому ця кількість лінійно зростає із збільшенням розрядності перетворюваного слова.

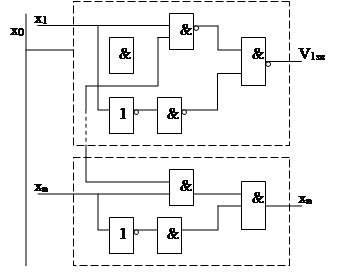

Функціонально схему для n=4 можна представити у вигляді:

Для реалізації багато розрядних схем також використовують регулярні структури, виконані на більш простих оптимізованих елементарних схемах.

Для регуляризації такої структури зручно виділити елементарні перетворення для і-того розряду.

Логічні функції для елементарних комірок можна описувати співвідношеннями:

Таким чином в кожному наступному каскаді регулярної структури як вхідний використовується вихідний сигнал з попереднього каскаду.

Принципова схема може бути реалізована з використанням складних елементів – двох І-АБО.

L=6(n-1) – складність схеми.

K=15(n-1) – вартість за Квайном.

t=(n+1)t3 – час затримки.

Комбінаційні схеми перетворення чисел з однієї системи числення в іншу використовуються для шифрування інформації і узгодження різних позиційних систем.

4. Комбінаційні суматори. Їх класифікація. Таблиці істинності та схемотехнічна реалізація напівсуматора. Синтез повного однорозрядного та n-розрядного суматора

Суматором називається пристрій, призначений для виконання арифметичних операцій з числами, представленими у двійковій формі.

![]()

![]()

Класифікують суматори за розрядністю чисел, над якими виконують операції, на напівсуматори, одно- та багаторозрядні суматори; за структурною схемою – на послідовні, паралельні та послідовно-паралельні; за функціонуванням – на синхронні та асинхронні, в залежності від часу затримки проходження сигналів різних каскадів.

Схемотехнічно суматори зображаються у вигляді комбінаційних схем або цифрових автоматів.

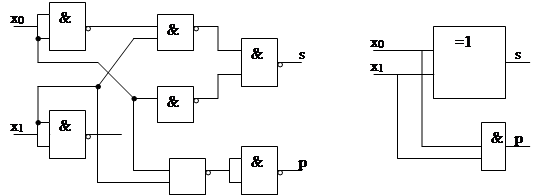

Комбінаційним напівсуматором називається пристрій, що має два входи, на які подаються операнди, і виходи результату (суми) та знаку переносу в наступний розряд.

Функціонування описується таблицею істинності аналогічної до суми за модулем 2 (s – сума, p- знак переносу).

| x0 |

x1 |

s |

p |

| 0 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 1 |

1 |

0 |

1 |

Як видно із таблиці істинності величина арифметичної суми відрізняється від знаку переносу типом логічної функції:

![]()

Параметр s записується і схемотехнічно виконується за допомогою логічного елемента виключне АБО, а параметр р реалізується коміркою елементарного кон’юнктора. Використовують базовий набір І-НЕ або функціональну комірку виключного АБО (К155АП5). Схему такого суматора можна представити наступним чином:

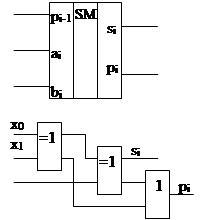

Для реалізації повного суматора необхідно враховувати знак переносу з попереднього розряду. Функціональна комірка повинна отримати додатковий вхід.

Схемотехнічно такий пристрій реалізується за допомогою двох базисних елементів виключне АБО, один з яких виконує функцію множення за модулем 2 вхідних операндів, а другий до результату одержаної суми додає знак переносу з попереднього розряду.

Розряд переносу на виході одержується шляхом диз’юнкції знаків переносу з обох комірок напівсумування.

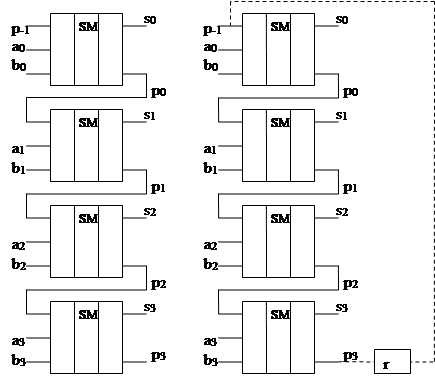

Повним n -розрядним суматором називається арифметичний пристрій, що забезпечує додавання двох n-розрядних двійкових слів і містить 2n+1 вхід та n+1 вихід. Збільшення розряду входу і виходу на одиницю дозволяє рахувати результат переносу, як з попереднього, так і з наступного розряду.

Найпростіше таку схему реалізувати у вигляді послідовної комбінаційної схеми, виконаної у вигляді каскадного нарощування одно розрядних повних суматорів.

В схемах звичайного сумування на вхід р-1 подається нульове значення, однак часто при виконанні арифметичних операцій доводиться виконувати циклічне зміщення двійкового коду. В цьому випадку використовується кільцевий n-розрядний суматор, у якому на вхід першого розряду подається сигнал знаку переносу останнього розряду через певну ланку затримки.

При паралельно-послідовному сумуванні n-розрядні слова х та у розбивають на m-розрядні підслова. На схему суматора m-розрядного підслова послідовно в часі подаються двійкові коди. Запис і зчитування результатів сумування відбуваються послідовно, а арифметичні операції з кожними підсловами реалізуються паралельно.

Функціонально при реалізації однорозрядного суматора з допомогою логічних функцій можна одержати запис суми та переносу ДДНФ:

Як видно із запису функція si може бути представлена у вигляді конституєнт одиниці, жодна пара з яких не може бути склеєна, тоді як результат переносу представляється у спрощеному вигляді диз’юнкції попарних кон’юнкцій всіх аргументів. Таку схему реалізовують з допомогою складних логічних елементів типу І-АБО-НЕ чи АБО-І-НЕ.

5. Схемотехнічні різновидності тригерів. Асинхронний та синхронний RS-тригери. Їх таблиці істинності, вихідні функції і структура

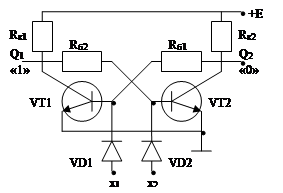

Тригери – це цифрові пристрої, що здатні формувати два стійких логічних стани, а також зберігати їх протягом певного моменту часу, що визначається умовами функціонування.

Такі системи реалізують на основі ключових елементів з використанням схем зворотного зв’язку. В найпростішому випаду – це два електронних транзисторних ключі, ввімкнені за схемою із 100% зворотнім зв’язком за постійною складовою керуючого сигналу.

Бі-стабільна комірка на основі двох ключів при початковому ввімкненні за рахунок незначного переважання колекторного струму в одному з плечей переходить в стійкий стан, при якому одне плече повністю відкривається і вихідний сигнал на ньому прямує до логічного нуля, а інша закривається – на виході логічна одиниця. Для переведення системи в протилежний стан на закритий ключ потрібно подати вхідний сигнал високого рівня. Така схема є аналогом найпростішого RS-тригера.

Тригери класифікують за функціональними особливостями, які відображаються в їх умовних позначеннях та найменуваннях кодів.

Вхід S – установка (Set);

Вхід R – обнулення (Reset);

Вхід K – обнулення універсального тригера;

Вхід J – установка універсального тригера;

Вхід T – лічильний вхід;

Вхід D – інформаційний або вхід затримки (Delay);

Вхід C – синхронізація;

Вхід V- ключовий вхід.

Відповідно розрізняють RS, JK, VD, VT, D, T – тригери.

За наявністю сигналу синхронізації тригери бувають синхронні та асинхронні, тобто такі, які перемикаються при подачі інформаційного сигналу або тільки при наявності сигналу синхронізації С.

За видом сигналу керування розрізняють статичні та динамічні тригери, які працюють за потенційним рівнем сигналу або за його перепадом.

За кількістю каскадів розрізняють одно- та двоступеневі тригери.

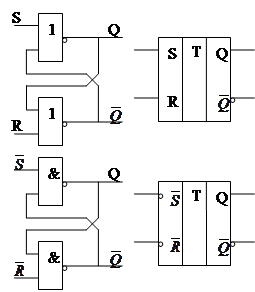

Асинхронний RS -тригер

Найпростіше реалізувати на базових елементах АБО-НЕ та І-НЕ. На елементах АБО можна одержати тригер з прямими керуючими входами, на елементах І-НЕ – з інверсними.

Функціонування тригера як ЦА також описується таблицями істинності та логічними функціями, однак потрібно враховувати динаміку зміни інформаційних сигналів в різні моменти часу, тобто вихідні сигнали аналізуються в попередній та наступний моменти часу.

Перехід із 0 в 1 здійснюється за керуючим сигналом 1 на вході S прямого та вході 0 інверсного тригера. Обнулення реалізується по входу R, але при цьому мають бути дозволяючи сигнали на входах Reset. Установка в одиничний стан обох входів RS-тригера або в нульовий інверсного тригера є забороненою, що відображається в таблиці істинності.

| Qt |

Qt+1 |

R |

S |

|

|

| 0 |

0 |

- |

0 |

- |

1 |

| 0 |

1 |

0 |

1 |

1 |

0 |

| 1 |

0 |

1 |

0 |

0 |

1 |

| 1 |

1 |

0 |

- |

1 |

- |

Таблиці істинності не повного представлення про динаміку зміни сигналу, для цього використовуються потенційні діаграми.

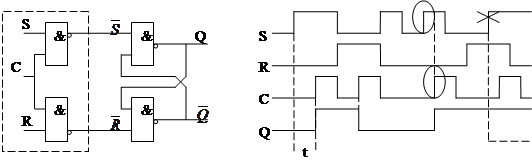

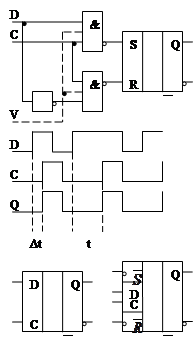

Синхронний RS -тригер

Синтезується на основі асинхронного з допомогою додавання вхідного каскаду, який забезпечує синхронізацію подачі керуючих сигналів на вихідний каскад.

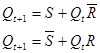

Алгоритм роботи цього тригера аналогічний асинхронному, однак запис і обнулення інформації здійснюється тільки за наявності тактового сигналу С, оскільки це потенційний пристрій, то перемикання відбувається за переднім фронтом сигналу синхронізації. Логічна функція враховує як стани вихідного, так і вхідного каскаду:

![]()

Використовуючи трьохвходові елементи у вихідному каскаді можна реалізувати одночасно синхронний RS-тригер з прямою логікою роботи та асинхронний з інверсною логікою.

В такій схемі вищою пріоритетністю володіють інверсні входи керування, що знаходяться у вихідному каскаді. Подання логічної одиниці на вхід синхронізації С переводить схему в асинхронний режим роботи.

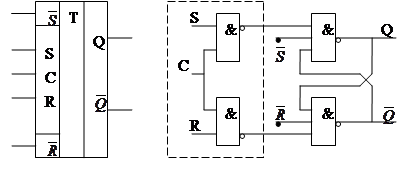

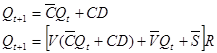

6. D- і Т-тригери. Їх таблиці істинності, вихідні функції і структура. Двоступеневі тригери

D -тригер

D-тригер містить інформаційний D-вхід та вхід синхронізації. Його зручно синтезувати з допомогою синхронного RS-тригера, якщо інформаційний сигнал D подати на вхід S, а на R-вхід подати його інверсію.

Алгоритм роботи схеми описується логічним твердженням: вихідний сигнал Q повторюватиме інформаційний сигнал D, але тільки при наявності сигналу синхронізації С.

Затримка сигналу на виході на інтервал часу t визначається зсувом фаз подання сигналів D та С.

Потенційна діаграма роботи зображена на малюнку.

Часто використовують RS та D-тригер розміщені в одному корпусі.

Якщо на вхідний каскад додатково ввімкнути вхід V, використовуючи трьохвходові кон’юнктори із запереченням, то реалізується VD-тригер.

Сигнал V забезпечує блокування вихідного сигналу аналогічно до сигналу синхронізації С і приводить до зміни функціональної залежності.

Т-тригер

Реалізується найпростіше на основі інформаційного або RS-тригера з синхронізуючим входом, якщо в D-тригері інверсний сигнал з виходу подати на вхід або в RS-тригері реалізувати потрійний зворотній звязок.

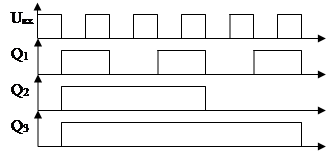

Логіка роботи Т-тригера: вихідний сигнал Q змінює свій стан на протилежний за кожний вхідний тактовий імпульс Т. Таким чином реалізується поділ тактової частоти двічі.

Реальні схеми Т-трігерів в найпростішому вигляді є непрацездатними. Це обумовлено суміщенням функцій комутації та зберігання даних фактично в одній точці схеми (Т – закорочення виходу і входу). Розв’язують цю суперечність, використовуючи додаткові затримки в колах зворотного зв’язку або двоступеневі тригери.

7. Паралельні регістри та регістри зсуву. Їх структурні схеми, класифікація, різновидності, функціонування

Регістрами називають послідовні цифрові автомати, призначені для запису, зберігання та відтворення багато розрядних двійкових кодів. Використовуються в цифрових ЕОМ для зберігання та відтворення багато розрядних двійкових кодів, а також для зберігання тимчасових значень операндів, непрямих адресних звертань та ін.

Класифікують їх за:

1. методом запису інформації:

- послідовні

- паралельні

- універсальні

2. за методом керування записом:

- синхронні

- асинхронні

3. за кількістю сигналів, що використовуються для керування:

- однофазні

- парафазні

4. за основним призначенням:

- регістри пам’яті

- регістри зсуву

Будують регістри на основі періодичних структур, кількість яких визначається розрядністю запам’ятовуючих слів. Структурно вони складаються з елементів памяті та комбінаційних схем керування. Останні забезпечують синхронний запис та зчитування інформації, обнулення та ін. В багато контактних схемах застосовуються двоступінчасті тригери, які комутуються з допомогою динамічних сигналів, тобто з допомогою динамічних перепадів логічних 0 та 1.

Паралельні регістри

Паралельні регістри синхронного та асинхронного типу найпростіше синтезувати на основі паралельного ввімкнення RS-тригерів. При цьому сигнал тактового запису та обнулення запаралелюється, а інформаційні входи призначаються для паралельного подання на них потрібних кодових слів.

Запис всіх біт інформації здійснюються за допомогою одного тактового імпульсу. Якщо для обнулення інформації чи запису використати парафазні сигнали, які подаються на кожен біт (тригер) окремо, то кажуть, що така схема працює за парафазною схемою керування. Для одержання нового інформаційного слова в інверсному вигляді можна використовувати інверсні Q виходи тригерів. Аналогічно для реалізації двофазної схеми паралельного регістра можна використати інформаційні D-тригери. В такому регістрі сигнали реалізації теж запаралелені.

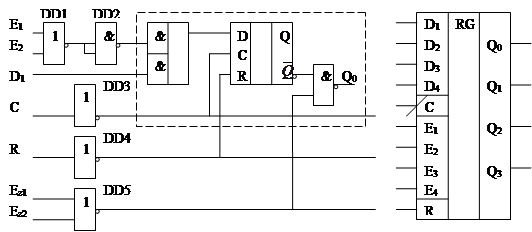

В якості елементів пам’яті використовують комірки на основі складних елементів 2, 2І-АБО, а також D-тригери, в яких реалізовано зворотній звязок для двох ступенів. Сигнали синхронізації (С) та обнулення (R) запаралелені для всіх комірок і подаються на відповідні входи D-тригерів. Дозвіл запису вхідних інформаційних сигналів D забезпечується керуючими сигналами Е1 , Е2 , ввімкненими за схемою АБО з додатною інверсією входу. Вхідні елементи DD1 та DD2 дозволяють розділити режими запису та зберігання інформації. Сигнали Ez 1 i Ez 2 також ввімкнені за схемою диз’юнкції при інверсії і забезпеченні переведення входів регістру Qi у високоімпедансний стан.

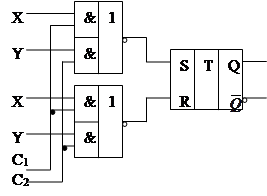

Для запису сигналів з різних джерел можна використовувати комбінаційні схеми 2, 2І-АБО, які забезпечують синхронізацію подачі сигналів S та R на комірки пам’яті. Керування комутацією різних джерел реалізується з допомогою двопозиційного коду С1 С2 .

В залежності від двійкового коду С1 С2 на вхід установки комірки регістру подається вхідний сигнал Х або У. синхронно з ним інверсні сигнали записуються на вхід R. Розрядність нарощування регістрів не обмежується за кількістю інформаційних сигналів, однак в реальних схемах потрібно враховувати допустимі значення коефіцієнтів розгалуження за виходом базових логічних елементів, що застосовуються в комбінаційних схемах керування, щоб не допустити зменшення вихідного рівня сигналу за мінімальне значення логічної одиниці.

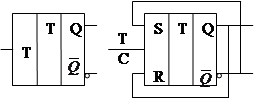

Регістри зсуву

В схемах зсуву запис багаторозрядного коду розрядністю n здійснюється за n тактів синхронізації. При цьому найстарший біт постійно перезаписується в усі комірки багаторозрядного регістра. Схему такого регістра можна реалізувати з допомогою базових комірок на основі комбінаційних RS та D-тригерів.

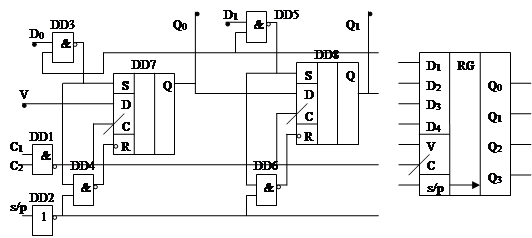

Режим роботи схеми визначається сигналом, що подається на вхід s/p (мікросхема DD2). При нульовому значенні s/p інвертор DD2 подає логічний рівень 1 на DD4, DD6. Це забезпечує інвертування сигналу на входах R, що дозволяє проходження паралельного двійкового коду інформаційних входів D0 , D1 на входи установки RS-тригерів. Запам’ятовування інформації здійснюється за тактовим перепадом імпульсу на входах з високого до низького рівня. Наявність DD4, DD6 забезпечує неоднозначність сигналів на RS-входах. Зміна вхідного s/p сигналу приведе до блокування входів D0 , D1 і запис інформації можливий з інформаційного входу V, з’єднаного з D-входом інформаційного тригера DD7. За такт перепадом синхроімпульсу С інформація з виходу Q DD7 записується на вхід DD8. Таким чином реалізується послідовний зсув інформації за кожним тактовим імпульсом на одну позицію вправо.

Розрізняють одно- та двонаправні регістри зсуву. В перших реалізується на схемотехнічному рівні зсув тільки вліво або тільки вправо. В других схемотехніка дозволяє з допомогою програмованого входу реалізувати зсув чи вліво, чи вправо. В умовних позначеннях це відображається стрілкою.

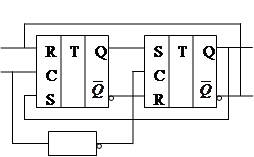

8. Класифікація, різновидності, функціонування лічильників. Переваги та недоліки послідовних і паралельних схем лічильників. Їх швидкодія і складність. Двійкові та двійково-кодовані лічильники

Лічильниками називаються послідовні логічні пристрої, призначені для перерахунку кількості імпульсів, а також для зберігання цієї інформації в двійковому коді. Будують їх на основі динамічних Т-трігерів. В залежності від схеми комутації тригерів та комбінаційної схеми керування лічильники можуть забезпечувати як додавання одиничних імпульсів, тобто виконання функцій інкрименту, так і віднімання – функція декрименту.

До основних параметрів лічильників відносять модуль перерахунку та час встановлення вихідного двійкового коду. За модулем перерахунку їх поділяють на двійкові ( М = 2n ) та двійково-кодовані, наприклад, двійково-десяткові, тобто з нецілочисельним модулем М. За напрямком перерахунку: лічильники з додаванням, відніманням та реверсивні.

За способом організації міжкаскадних зв’язків виділяють лічильники з послідовним, паралельним та комбінованим переносом.

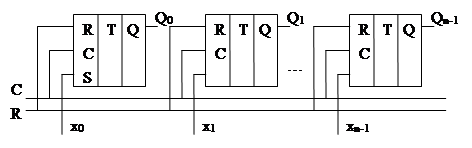

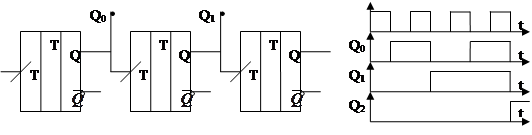

Найпростіше реалізовуються схеми з послідовим переносом на динамічних Т-тригерах. В цьому випадку вихід попереднього каскаду вмикається на вхід наступного.

Для побудови додаючого лічильника використовується інверсія стану в лічильному тригері. Якщо в якості прямого сигналу використовується прямий вихід Т-тригера Q, то динамічний вхід його повинен бути з переходом в активному стані від 1 до 0 і , навпаки, при прямому динамічному вході для одержання функції додавання необхідно використовувати інверсний вихід тригера , тільки у цьому випадку активними станами будуть нульові стани.

Якщо використати однойменні вхідні-вихідні сигнали, то реалізується функція віднімання, епюри напруг якої зображені на малюнку.

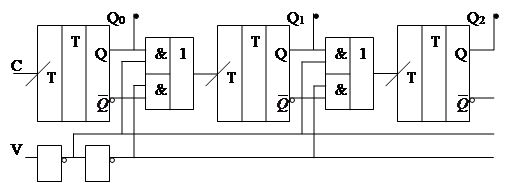

Таким чином, досить просто реалізувати реверсивний лічильник, використовуючи змінну комутацію вихідного сигналу при постійному значенні динамічного входу. Для цього звичайну схему динамічного лічильника доповнюють елементами складної логіки 2,2 І-АБО. Схема керування доповнюється двома інверторами , які забезпечують пере комутацію сигналів з виходів складних елементів.

Сигнал V визначає напрямок перерахунку додавання чи віднімання. Вхідні тактові імпульси подаються на вхід С першого тригера . Якщо V = 1, то на перший елемент І комбінаційного пристрою 2,2 І – АБО подається значення логічного нуля, на другий – значення логічної одиниці, тобто в цьому випадку інформаційним сигналом є сигнал з інверсного виходу ![]() тригера. При прямому динамічному вході реалізується схема додавання.

тригера. При прямому динамічному вході реалізується схема додавання.

Якщо V = 0, активним стає прямий вихід тригера і маємо реалізацію схеми віднімання.

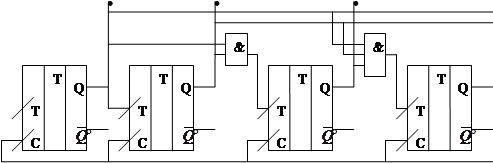

При реалізації схеми віднімання, якщо маємо обтулені значення Q за першим тактовим імпульсом, в тригер записується максимальне значення коду – всі одиниці і з кожним тактовим імпульсом проводиться віднімання по одному двійковому числу. Загальним недоліком є зростання часу комутації результуючого вихідного стану лічильника при зростанні загальної його розрядності. Для усунення цього недоліку використовуються лічильники з паралельним переносом, тоді схеми послідовних лічильників доповнюють комбінаційними елементами, які враховують в кожному наступному розряді стани всіх попередніх розрядів, що реалізуються функцією кон’юнкції.

Обов’язковою умовою схем паралельного переносу є використання синхронізуючого С – входу. Недоліком є зростання числа входів в кон’юнкторах із зростанням розрядності лічильника, оскільки вони повинні забезпечувати реалізацію функції множення за модулем 2.

Для І розряду формуючий сигнал залишається асинхронним, тому його приймають рівним 1. В лічильнику з паралельним переносом напрямок перерахунку не залежить від вибору типу вхідного стану (прямого чи інверсного), він визначається тільки використаними вихідними сигналами Q або ![]()

![]() , тому реалізувати реверсивну схему можна аналогічно до схеми послідовного лічильника. Для усунення недоліків паралельних схем і підвищення швидкості перерахунку використовуються комбіновані схеми паралельно-послідовного переносу, при цьому лічильник розрядності n, меншої за загальну розрядність m лічильника, є базовою групою, в якій реалізовано паралельний підрахунок. Передача комутаційних сигналів між групами реалізується послідовно.

, тому реалізувати реверсивну схему можна аналогічно до схеми послідовного лічильника. Для усунення недоліків паралельних схем і підвищення швидкості перерахунку використовуються комбіновані схеми паралельно-послідовного переносу, при цьому лічильник розрядності n, меншої за загальну розрядність m лічильника, є базовою групою, в якій реалізовано паралельний підрахунок. Передача комутаційних сигналів між групами реалізується послідовно.

Максимальне значення часу перемикання визначається часом комутації тригерів у окремій групі. При цьому потрібно враховувати загальний максимальний час, який залежить від кількості груп багаторозрядного лічильника l:

t під. ьакс. = t зр. ( l – 1 ).

В загальному випадку кількість тригерів в кожній групі може бути довільною і навіть рівною 1, тому паралельно-послідовну схему можна реалізувати для окремих розрядів, Така схема називається схемою з наскрізним переносом.

В такій схемі комутація тригерів відбувається практично одночасно, необхідно враховувати тільки час затримки на комутацію одного окремого розряду із врахуванням часу затримки в комбінаційній схемі. Підвищення швидкодії досягається за рахунок того, що час перемикання комбінаційної схеми менший за час комутації тригера.

9. Керуючі автомати АЛП. Синтез керуючих автоматів зі схемною логікою. Структурна схема та алгоритм структурного синтезу автоматів зі схемною логікою

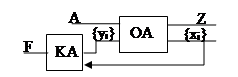

Арифметико – логічним пристроєм називаються функціонально завершені вузли ЕОМ і призначені для використання арифметичних операцій та логічної обробки даних, які представлені у вигляді двійково-кодованих інформаційних сигналів. Такі вузли можна реалізувати за допомогою схемотехнічних пристроїв, функціонування яких визначається на апаратному або програмному рівні, тобто в пристроях з жорсткою або програмованою логікою. В загальному випадку АЛП складаються з операційного та керуючого автоматів.

Операційний автомат призначений для безпосереднього виконання арифметичних операцій, згідно керуючих сигналів {yi }, та даних А, які на нього поступають. Результат виконання операцій індукується на Z-виходах. Сукупність вихідних сигналів {xi } несе інформацію про отримані результати та разом з вхідними керуючими сигналами F формує сигнали мікрокоманд yi .

Синтез керуючих автоматів зі схемною логікою

Основі синтезу структури таких автоматів розроблені академіком Глушковим.

Згідно канонічного методу, структурний синтез описується законами функціонування абстрактного автомату, який реалізується з допомогою комбінаційних схем та наборів тригерів – RS, JK, D, T. Тригери є елементарними автоматами, реалізованими за принципом Мура. Вони характеризуються двома логічними станами, що дозволяють описати їх двозначним структурним алфавітом і є основою для побудови пристроїв зі схемною логікою.

![]()

Алгоритм структурного синтезу керуючих автоматів зі схемною логікою може бути наступним:

1. розробка мікропрограми і її запис на мові мікрооперацій;

2. побудова змістовного графа та закодованого графа;

3. розмітка графа мікропрограми для певного типу автоматів з метою одержання числа станів пам’яті, необхідної для реалізації даної мікропрограми;

4. побудова графа вибраного автомата та його розмітка;

5. кодування станів пам’яті автомата двійковими наборами станів Qi ;

6. побудова комбінаційної частини автомата на основі функціональних таблиць і графів.

10. Синтез керуючих автоматів з програмованою логікою. Класифікація мікропрограм КА. Горизонтальне, вертикальне та комбіноване кодування мікрокоманд і методи їх адресації

Такі автомати будують на основі операційно-адресної структури з використанням загальних принципів програмного керування. Алгоритмом керування є впорядкований набір керуючих слів мікрокоманд, які визначають порядок функціонування дискретного пристрою потягом машинного циклу. Сукупність з р- і к- розрядних мікрокоманд створює загальний масив, що зберігається в пам’яті цифрового автомату.

Структурна схема автомату з програмованою логікою включає: вузол адресації, що складаються з формувача адреси мікрокоманд (ФАМК); регістра мікрокоманд з дешифратором адреси; вузла пам’яті ПМК; регістра мікрокоманд, який отримує інформацію про тип операції у, що повинна виконуватись в даному циклі; сукупності логічних умов х, які описують алгоритм виконання операції і характеризують одержані результати, а також адресу наступної операції.

Керуючі сигнали у після дешифрації мікрооперацій у вузлі дешифратора DСМО подаються в операційну частину арифметично-логічного пристрою.

Мікропрограмовані керуючі автомати класифікують:

1. За типом пам’яті для зберігання мікрокоманд:

статичні, динамічні, постійні;

2. За способом кодування мікрооперацій: горизонтальні, вертикальні, комбіновані;

3. За часом виконання: синхронні, асинхронні, однофазні, багатофазні;

4. За способом адресації: з послідовною вибіркою, з примусовою вибіркою, з довільною вибіркою.

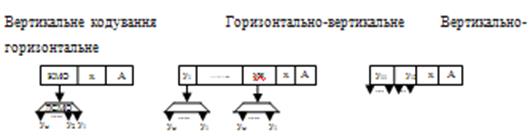

При горизонтальному кодуванні поле мікрокоманди містить М розрядів:

![]()

Кількість розрядів визначається числом мікрооперацій, що задає дана команда. Перевагою такого кодування є можливість одночасного виконання в одному такті машинного циклу мікрокоманди з довільним набором М мікрооперацій. Однак при цьому довжина мікрокоманди є досить велика і в певних пристроях мікрокоманда потребує кількох тактів завантаження.

Вертикальне кодування передбачає шифрування всієї множини М мікрооперацій двопозиційним кодом. Довжина коду визначається кількістю мікрооперацій: ![]()

Для визначення набору операцій додатково потрібно використовувати дешифратор мікрооперацій.

Горизонтально-вертикальне кодування передбачає розділення всієї множини у команд на Н полів. В кожному полі розміщена множина із М операцій. Комірки, тобто всі поля кодуються вертикально. Це означає, що кожне поле має зв’язок з окремим дешифратором мікрооперацій. Відповідно максимальне число мікрооперацій буде Н. Мікрооперації уі дешифруються горизонтально. Реально тут використовуються переваги вертикального методу, пов’язані з коротшою довжиною декодуючого слова. Недолік, зумовлений меншою швидкодією, також залишається.

При вертикально-горизонтальному кодуванні вся довжина мікрооперацій М розділена на к підмножин. В кожній з цих підмножин об’єднуються операції, які найчастіше зустрічаються в одному машинному такті. Операційна частина мікрокоманди складається з двох полів: у11 та у12 . у11 використовує горизонтальний спосіб кодування, а поле у12 показує до якої підмножини належить мікрокоманда, записана у першому полі.

Послідовні вибірки адрес забезпечують лічильником адрес мікрокоманд, вміст якого збільшується на 1 після виконання кожної поточної мікрокоманди. В адресній мікрокоманді записані 3 параметри:

- значення логічної умови х

- значення безумовного переходу БП

- значення адреси.

11. Центральний пристрій керування. Структурна схема та алгоритм його роботи

ЦПК – це сукупність вузлів і блоків процесора, які забезпечують координацію функціонування всіх пристроїв машини для всіх заданих її режимів роботи. ЦПК реалізує системні і робочі програми, організовує перетворення початкової інформації для одержання результатів обчислень. Функціональна схема ЦПК включає пульт керування, операційну пам’ять, АЛП, регістр команд, лічильник адреси команд, керуючі мікропрограмні автомати, дешифратори коду операцій та операційний блок, що містить суматор адреси, схеми аналізу режимів роботи, інтерфейсні схеми та інше.

![]()

Алгоритм роботи ЦПК визначає послідовність команд для реалізації арифметичної та логічної обробки даних, що активізуються певними вузлами системи. Запуск системи здійснюється з пульта керування, шляхом запису в лічильник адреси першої виконуваної команди. Значення цієї адреси подається в регістр адрес ОП, проводиться вибірка за адресою з пам’яті самої мікрокоманди, вибірка даних, і мікрокоманда записується в регістр мікрокоманд. В результаті виділення коду операції, після дешифрації цього коду, подаються сигнали керування на мікропрограмний апарат МПА1, якщо команда забезпечує керування системою, або МП2 – якщо необхідно виконати арифметичні операції. Одночасно розшифровується адреса наступної команди, яка подається у лічильник команд або в операційний блок.

12. Операційні апарати АЛП. Арифметичні вузли операційних апаратів. Вузли додавання-віднімання чисел у прямих і доповнюючих кодах, алгоритм їх роботи

Виконання будь-якої операції АЛП зводиться до виконання послідовності арифметичних та логічних дій, які ще називають мікроопераціями і виконуються вони на окремих операційних вузлах. Алгоритм виконання мікрооперацій можна описати з допомогою так званої нотації Бекуса. Як вказано раніше, формат команд включає умовні позначення, ідентифікатори операційних вузлів ти, власне, шифр відповідної арифметичної чи логічної дії. При цьому використовуються умовні позначення мікрооперацій, наприклад:

В1 , В2 , В3 – відповідно ввід прямого, інверсного або доповнюючого коду певного операнда;

П0 – установка операційного вузла в нульове значення;

П1 , П2 , П3 – завантаження (прийом) певного двійкового коду;

С1і , С2і – зсув слова у вигляді двійкового коду на і позицій вліво чи вправо;

Pi , Ri – додавання, віднімання від константи слова і.

Таким чином можна описати операції установки лічильника в нульове значення.

С24 RGY – вказує на необхідність зсуву вмісту регістра У на 4 позиції вправо.

R1

СТС – забезпечує віднімання одиниці від коду записаного в лічильник С. Логічні переходи за певною умовою описуються з допомогою вказання умови у вигляді виразу х та стрілки з певною міткою. ![]() вказує що при хn

=1 необхідно перейти на виконанна мікрооперації, розміщеної за міткою

вказує що при хn

=1 необхідно перейти на виконанна мікрооперації, розміщеної за міткою ![]() .

.

13. Додавання і відніманя чисел з плаваючою комою; алгоритм нормалізації порядку і заокруглення мантиси чисел

Операції такого типу зручно використовувати коли розмірності операндів мають однакові порядки, тобто кількість розрядів цілої і дробової частини в них однакова. Етапи реалізації мікрооперацій виконуються за наступною послідовністю:

1. проводять вирівнювання порядків;

2. додають мантиси;

3. визначають порядок результату;

4. проводять нормалізацію результату;

5. заокруглюють мантиси до потрібної кількості розрядів;

6. проводять кінцеву нормалізацію результату.

Одержану різницю порядків записують в лічильник. Якщо 0, то необхідно зсувати вправо числа у, якщо 0 - то числа х.

1. При кожному зсуві від різниці порядків () віднімають або додають одиницю, відповідно при, 0, та 0.

2. Вирівнювання порядків завершують, коли вміст лічильника порядків обтулюється. Мікроалгоритм вирівнювання порядків на мові мікрокоманд можна записати так:

0

![]()

Функціональна схема блоковирівнювання порядків складається з блоку вирівнювання, блоку сумування, блоку нормалізації результатів та цифрового пристрою для округлення одержаного результату.

![]()

Принцип дії схеми додавання/віднімання чисел з плаваючою крапкою відображено на функціональній схемі. Блок вирівнювання порядків (БВП) видає сигнал зсуву вправо на регістри RGX або RGY, які знаходяться в регістрах загального призначення блоку сумування мантис (БСМ), а також виводить результат порядку С в блок нормалізації результатів (БНР). На початку стану за сигналом запуску з БВП вмикається БСМ, за другим сигналом – БНР. За сигналом, що першим виробляється на виході БНР проводиться округлення результату, за другим сигналом з допомогою тригера генерується сигнал закінчення операції К.

14. Структурна організація запам’ятовуючих вузлів з 2D-структурою. Особливості дешифрації адресного коду у вузлах з 3D-структурою пам’яті

Методика дешифрації адресного простору в 2 D пам’яті

Для виділення окремих адрес комірок пам’яті в матриці, розмірністю Nxm використовується принцип буферизації адресного коду, який далі дешифрується і подаються на окремі рядки матриці. Для інформаційних сигналів окремо використовують буфер даних, розрядність якого повинна бути рівною кількості елементів у рядку. Структурну схему при такій організації можна зобразити наступним чином:

При звертанні до пам’яті в даному випадку вибирається (активується) рядок, номер якого відповідає вибраній адресі, а кожен біт з цього рядка зчитується за сигналом Read / Write.

Умовно це можна зобразити так:

![]()

![]()

3 D структурна пам’ять

![]()

![]()

Поділ загального адресного простору на 2 частини потребує відповідного збільшення у 2 рази буферних вузлів та дешифраторів, але перехід до об’ємної організації дозволяє зменшити розрядність буферних регістрів, а також зменшити складність дешифраторів. Матриця комірок пам’яті має організацію mx(rxr), де r – це величина півслова, яка визначається дешифрацією півслова, тобто двійкового слова, розрядністю к/2.

Організацію підматриці mx(rxr) можна показати у вигляді двовимірного масиву.

Зменшення складності дешифраторів досить суттєве. Наприклад, якщо для адресації 1кб пам’яті в 2D структурі потрібен вихідний унітарний код, розмірністю 1024 позиції, то в 3D структурі достатньо використати два 32-розрядні вихідні коди з дешифраторів DCX і DCY. Недоліком такої пам’яті є необхідність застосування комірок елементів пам’яті, що допускають подвійну адресацію.

15. Порівняльна характеристика суперскалярних мікропроцесорів з CISC та RISC архітектурою

CISC-архітектура - архітектура з повним набором команд (CISC – Complete Instruction Set Computer) володіє такими властивостями:

· невелика кількість регістрів загального призначення;

· велика кількість типів машинних інструкцій;

· наявність команд, навантажених семантичним значенням, подібним до операторів високорівневих мов програмування; такі команди виконуються за декілька машинних циклів (тактів);

· велика кількість методів адресації;

· велика кількість форматів команд різної розрядності;

· наявність команд обміну даними між регістрами і пам’яттю;

· переважає двоадресний формат команд.

RISC-архітектуру мають комп’ютери із скороченим набором команд (RISC – Reduced Instruction Set Computer).

Основні властивості комп’ютерів з такою архітектурою:

· велика кількість регістрів загального призначення;

· використання команд фіксованої довжини з малою кількістю типів форматів;

· регулярність, що дає змогу завдяки простоті команд виконувати одні й ті самі апаратні пристрої для виконання майже всіх команд;

· виконання більшості команд за один такт; підвищення швидкості досягається за рахунок апаратної реалізації виконання команд (на відміну від мікропрограмної);

· орієнтованість на регістри – всі операції з даними виконуються у регістрах, крім команд завантаження та запису, здійснення яких пов’язане із зверненням до пам’яті.