Логічні елементи, що застосовуються в електронно-обчислювальній техніці

СОДЕРЖАНИЕ: КУРСОВА РОБОТА Логічні елементи, що застосовуються в електронно-обчислювальній техніці ЗМІСТ ТЕОРЕТИЧНА ЧАСТИНА ЛОГІЧНІ ЕЛЕМЕНТИ ТА ОСНОВНІ ВУЗЛИ ЕОМ .3КУРСОВА РОБОТА

Логічні елементи, що застосовуються в електронно-обчислювальній техніці

ЗМІСТ

ТЕОРЕТИЧНА ЧАСТИНА

ЛОГІЧНІ ЕЛЕМЕНТИ ТА ОСНОВНІ ВУЗЛИ ЕОМ.....................................3

1 Логічні елементи............................................................................................3

2 Тригери та їхні характеристики....................................................................5

3 Регістри..........................................................................................................11

4 Лічильники....................................................................................................14

5 Перетворювачі кодів....................................................................................21

6 Суматори.......................................................................................................29

ПРАКТИЧНА ЧАСТИНА

1 Обґрунтування розвязку завдання..............................................................32

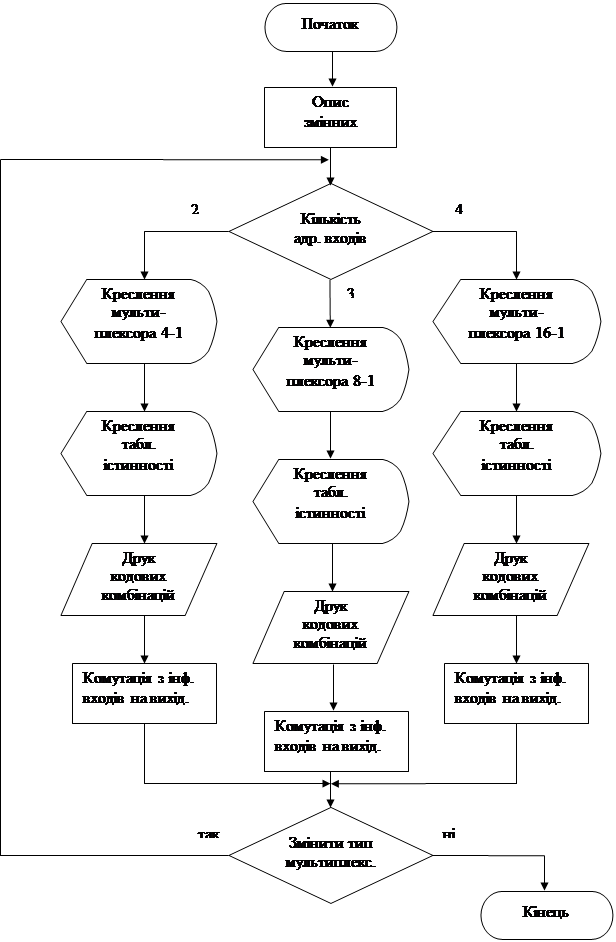

2 Граф-схема алгоритму..................................................................................33

3 Вказівки користувачеві.................................................................................34

4 Вказівки програмісту....................................................................................34

ВИСНОВКИ.............................................................................................................34

СПИСОК ВИКОРИСТАНОЇ ЛІТЕРАТУРИ.........................................................35

Додаток А.................................................................................................................36

ТЕОРЕТИЧНА ЧАСТИНА

ЛОГІЧНІ ЕЛЕМЕНТИ ТА ОСНОВНІ ВУЗЛИ ЕОМ

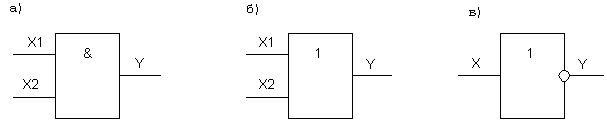

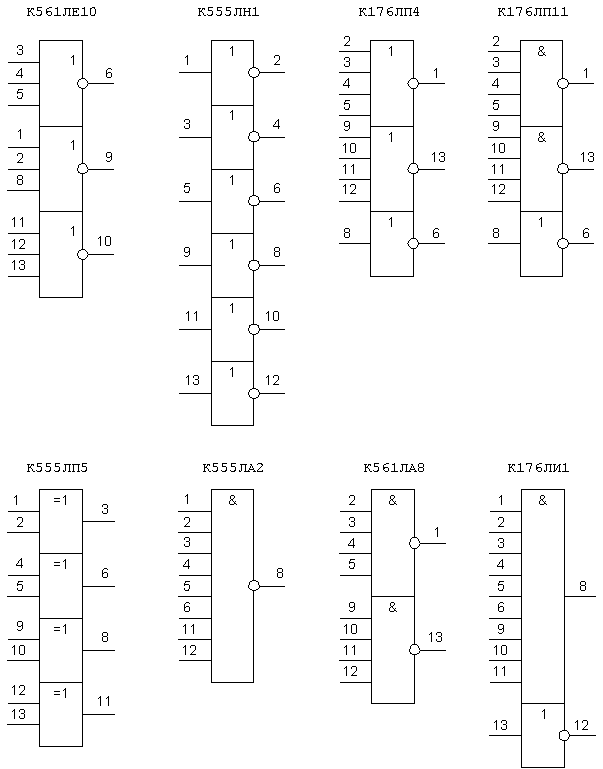

1 ЛОГІЧНІ ЕЛЕМЕНТИ

Логічний елемент - це електронний прилад, що реалізує одну з логічних функцій. В склад серій мікросхем, що розглядаються, входить велике число логічних елементів. На принциповій схемі логічний елемент зображають прямокутником, всередині якого ставиться зображення покажчика функції. Лінії з лівої сторони прямокутника показують входи, з правої - вихід елемента. На рисунку 1 зображені основні логічні елементи, що використовуються у цифрових приладах:

Елемент І (конюктор);

![]() (a)

(a)

елемент АБО (диз’юнктор)

![]() (б);

(б);

елемент НІ (інвертор 1)

![]() (в).

(в).

Окрім означених існує множина логічних елементів, що виконують більш складні логічні перетворення. Ці перетворення є комбінаціями найпростіших логічних операцій. До числа таких елементів відносяться:

елемент І-НІ ![]()

елемент АБО-НІ ![]()

елемент І-АБО ![]()

елемент І-АБО-НІ ![]()

суматор за модулем 2 ![]()

Рисунок 1 - Графічні позначення логічних елементів

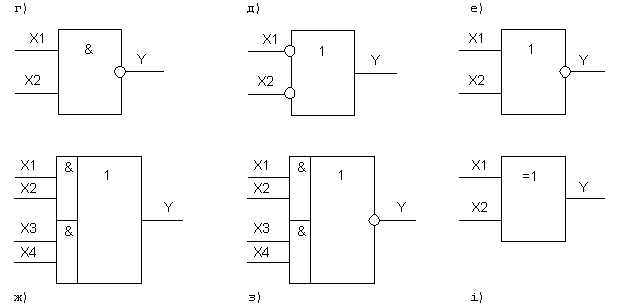

Суматор за модулем 2 можна виконати на логічних елементах І, АБО, НІ (рисунок 2).

Рисунок 2 - Схема суматора за модулем 2

Число входів в логічних елементах різного призначення може бути різним, але входи кожного елемента рівнозначні. Деякі з них можуть при роботі в конкретних приладах не використовуватися. Входи, які не використовуються в схемах І, І-НІ зєднують із +Uдж. , а в схемах АБО, АБО-НІ, суматора за модулем 2 - із загальним проводом (0 В).

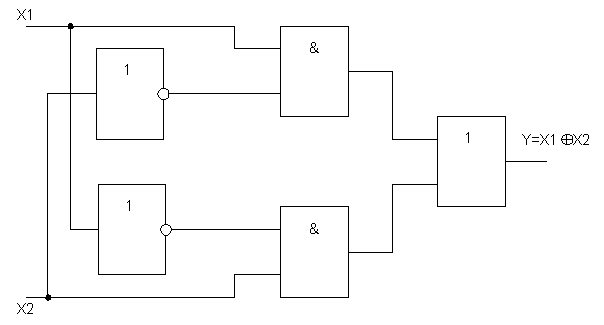

На рисунку 3 наведені приклади умовного позначення логічних елементів різних серій.

Рисунок 3 - Приклади графічного позначення логічних елементів різних серій

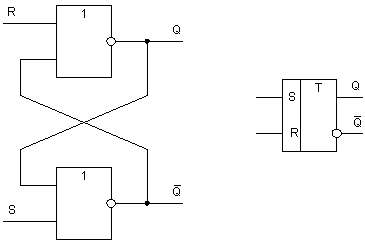

2 ТРИГЕРИ ТА ЇХНІ ХАРАКТЕРИСТИКИ

Найпростішими цифровими автоматами із памяттю є тригери. Тригер - це прилад послідовнісного типу з двома стійкими станами рівноваги, призначений для запису і зберігання інформації. Під дією вхідних сигналів тригер може переходити з одного стійкого стану в інший. При цьому напруга на його виході стрибкоподібно змінюється.

Як правило, тригер має два виходи - прямий та інверсний. Число входів залежить від структури і функцій, що виконуються тригером. За способом запису інформації тригери поділяють на асинхронні і синхронізовані (тактовані). В асинхронних тригерах інформація може записуватися безперервно і визначається інформаційними сигналами, діючими на входах у даний момент часу. Якщо інформація заноситься в тригер тільки в момент дії так званого синхронізуючого сигналу, то такий тригер називають синхронізованим або тактованим . Окрім інформаційних входів, синхронізовані тригери мають тактовий вхід (вхід синхронізації). В цифровій техніці прийняті такі позначення входів та виходів тригерів:

- Q – прямий вихід тригера;

- інверсний вихід тригера;

- інверсний вихід тригера; - S - роздільний вхід установки в одиничний стан (напруга високого рівня на прямому виході Q);

- R - роздільний вхід установки в нульовий стан (напруга низького рівня на прямому виході Q);

- D - інформаційний вхід (на нього подається інформація, призначена для занесення в тригер);

- С - вхід синхронізації;

- Т - лічильний вхід.

Найбільше розповсюдження в цифрових приладах отримали RS-тригер з двома установчими входами, тактований D-тригер і лічильний Т-тригер. Розглянемо функціональні можливості кожного з них.

Асинхронний RS-тригер. В залежності від логічної структури розрізняють RS-тригери з прямими і інверсними входами. Їхні схеми і умовні позначення наведені на рисунку 4. Тригери такого типу побудовані на двох логічних елементах: 2АБО-НІ - тригер з прямими входами (рисунок 4, а), 2І-НІ - тригер з інверсними входами (рисунок 4, б). Вихід кожного з елементів підєднаний до одного з входів іншого елемента, що забезпечує тригеру два стійких стани. Наведена таблиця 1.1 істинності для кожного з цих тригерів.

Рисунок 4 - Схеми та умовні позначення RS-тригерів

aftvin

Таблиця 1 - Таблиці істинності асинхронних RS-тригерів

| S |

R |

|

|

|

|

|

|

|

|

|

|

|

| 0 1 0 1 0 1 0 1 |

1 0 0 1 1 0 0 1 |

0 0 0 0 1 1 1 1 |

1 1 1 1 0 0 0 0 |

0 1 0 * 0 1 1 * |

1 0 1 * 1 0 0 * |

0 1 0 1 0 1 0 1 |

1 0 0 1 1 0 0 1 |

0 0 0 0 1 1 1 1 |

1 1 1 1 0 0 0 0 |

1 0 * 0 1 0 * 0 |

0 1 * 1 0 1 * 1 |

В таблиці 1 Qt і Qt позначають рівні, які були на виході тригера до подачі на його входи так званих активних рівнів. Активним називають логічний рівень, що діє на вході логічного елемента і однозначно визначає логічний рівень вихідного сигналу (незалежно від логічних рівнів, що діють на інших входах). Для елементів АБО-НІ за активний рівень приймають високий рівень, а для елементів І-НІ - низький рівень. Рівні, подача яких на один з входів не призводить до модифікації логічного рівня на виході елемента, називають пасивними . Рівні Qt+1 і Qt+1 позначають логічні рівні на виході тригера після подачі інформації на його входи. Для тригера з прямими входами Qt+1 = 1 при S= 1 і R= 0; Qt+1 = 0 при S= 0 і R= 1; Qt+1 =Qt при S= 0 і R= 0. При R=S= 1 стан тригера буде невизначеним (*), бо під час дії інформаційних сигналів логічні рівні на виході тригера однакові Qt+1 =Qt+1 , а після закінчення їхньої дії тригер може рівноймовірно прийняти будь-який із стійких станів. Тому така комбінація є забороненою.

Режим S= 1, R= 0 називають режимом запису 1 (бо Qt+1 = 1); режим S= 0 і R= 1 - режимом запису 0. Режим S= 0, R= 0 називається режимом зберігання інформації, бо інформація на виході залишається незмінною. Для тригера з інверсними входами режим запису логічної 1 реалізується при S= 0, R= 1, режим запису логічного 0 - при S= 1, R= 0. При S=R= 1 забезпечується зберігання інформації. Комбінація S=R= 0 є забороненою.

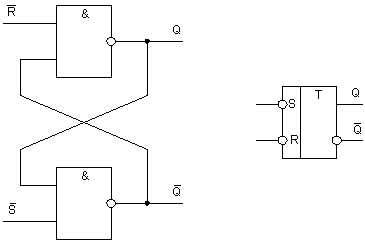

Тактовий D-тригер. Він має інформаційний вихід і вхід синхронізації. Одна із можливих структурних схем однотактного D-тригера і його умовне позначення наведені на рисунку 5.

Рисунок 5 - Схема та умовне позначення тактового D-тригера

Якщо рівень сигналу на вході С= 0, стан тригера стійкий і не залежить від рівня сигналу на інформаційному вході. При цьому на входи RS-тригера з інверсними входами (елементи 3 і 4) надходять пасивні рівні (S=R =1). При подачі на вхід синхронізації рівня С= 1 інформація на прямому виході буде повторювати інформацію, що подається на вхід D . Таким чином, при С= 0 Qt+1 =Qt , а при С= 1 Qt+1 =D (таблиця 2).

Таблиця 2 - Таблиця істинності тактового D-тригера

| D |

|

|

| 0 0 1 1 |

0 1 0 1 |

0 0 1 1 |

Тут Qt означає логічний рівень на прямому виході до подачі імпульсу синхронізації, a Qt+1 - логічний рівень на цьому виході після подачі імпульсу синхронізації.

В такому тригері відбувається затримка сигналу на виході по відношенню до сигналу, поданого на вхід, під час паузи між синхросигналами. Для стійкої роботи тригера необхідно, щоб протягом синхроімпульса інформація на вході була незмінною.

Тактові D-тригери можуть бути з потенційним і динамічним управлінням. У перших з них інформація записується протягом часу, при якому рівень сигналу С= 1. В тригерах з динамічним управлінням інформація записується тільки протягом перепаду напруги на вході синхронізації. Динамічні входи зображають на схемах трикутником. Якщо верхівка трикутника звернута в сторону мікросхеми, то тригер «спрацьовує» по фронту вхідного імпульсу, якщо від неї - по зрізу імпульсу. В такому тригері інформація на виході може бути затримана на один такт по відношенню до вхідної інформації.

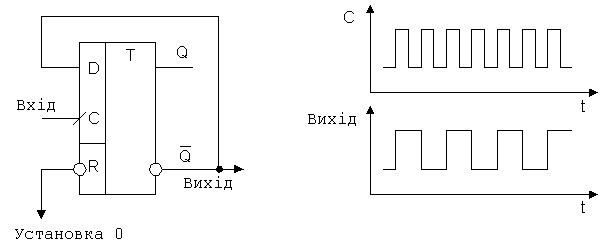

Лічильний Т-тригер (рисунок 6). Його називають також тригером зі лічильним входом. Він має один вхід керування Т і два виходи Q і Q . Інформація на виході такого тригера змінює свій знак на протилежний при кожному позитивному (або при кожному негативному) перепаді напруги на вході. В серії мікросхем, що випускаються, Т-тригерів, як правило, немає. Але тригер такого типу може бути створений на базі тактового D-тригера, якщо його інверсний вихід зєднати з інформаційним входом. Як видно з діаграми, частота сигналу на виході Т-тригера в два разу нижче частоти сигналу на вході, тому такий тригер можна використовувати як подільник частоти і двійковий лічильник.

Рисунок 6 - Лічильний тригер

В серіях мікросхем, що випускаються, є також універсальні JK-тригери. При відповідному підєднанні вхідної логіки JK-тригер може виконувати функції тригера будь-якого іншого типу.

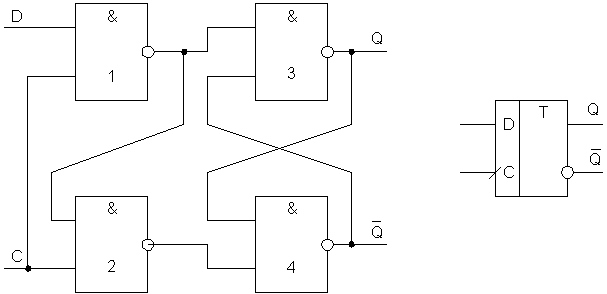

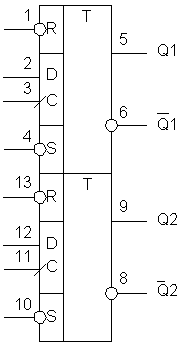

Умовні графічні позначення тригерів на принципових схемах наведені на рисунку 7.

Рисунок 7 - Графічні позначення тригерів

3 РЕГІСТРИ

Кілька тригерів можна обєднати в регістр - вузол для зберігання чисел з двійковим поданням цифр розрядів. Основними видами регістрів є паралельні і послідовні (зсувні).

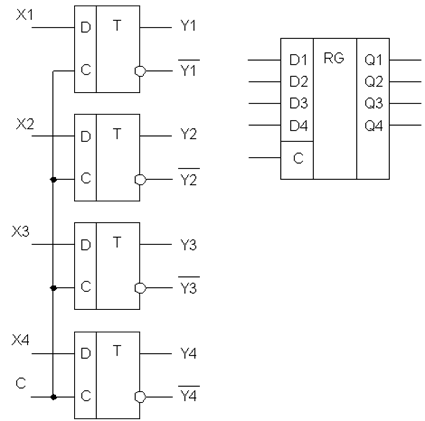

В паралельному регістрі на тактових D-тригерах (рисунок 8) код числа, що запам‘ятовується, подається на інформаційні входи всіх тригерів і записується в регістр з приходом тактового імпульсу. Вихідна інформація змінюється з подачею нового вхідного слова і приходом наступного імпульсу запису. Такі регістри використовують в системах оперативної памяті. Число тригерів в них дорівнює максимальній розрядності слів, що зберігаються у ньому.

Схема послідовного регістра і часова діаграма, що ілюструє його роботу, наведені на рисунок 9. З приходом тактового імпульсу С перший тригер записує код Х (0 або 1), що знаходиться в цей момент на його вході D, а кожний наступний тригер перемикається в стан, в якому до цього знаходився попередній. Так відбувається тому, що сигнал, який записується, проходить із входу D тригера до виходу Q із затримкою, більшою тривалості фронту тактового імпульсу (протягомі якого відбувається запис). Кожний тактовий імпульс послідовно зсуває код числа у регістрі на один розряд. Тому для запису N-розрядного коду необхідно N тактових імпульсів. На діаграмі видно, що чотирирозрядне число 1011 було записане у відповідні розряди регістра (1 - Q4, 0 - Q3, 1 - Q2, 1 - Q1) після приходу четвертого тактового імпульсу. До приходу наступного тактового імпульсу це число зберігається в регістрі у виді паралельного коду на виході Q4-Q1. Якщо необхідно отримати інформацію, що зберігається у послідовному коді, то її знімають із виходу Q4 в моменти приходу наступних чотирьох імпульсів (5-9). Такий режим називається режимом послідовного зчитування.

Рисунок 8 - Паралельний регістр на тактових D-тригерах

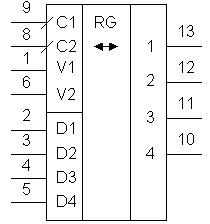

Дуже зручні універсальні регістри, що дозволять здійснювати як послідовний, так і паралельний запис і зчитування. Такі регістри можна використовувати як перетворювачі паралельного коду в послідовний і навпаки. Наприклад, мікросхема К555ИР1 (рисунок 10) - чотирирозрядний універсальний зсувний регістр. Регістр працює в режимі зсуву по тактових імпульсах, що надходять на вхід С1, якщо на вході V2 є напруга низького рівня. Вхід V1 служить для введення інформації в перший розряд регістра в цьому режимі. Якщо ж на вході V2 напруга високого рівня, то регістр здійснює паралельний запис інформації із входів D1-D4 по імпульсах синхронізації, що надходять на вхід С2.

Рисунок 9 - Послідовний регістр

Рисунок 10 - Чотирирозрядний зсувний регістр

4 ЛІЧИЛЬНИКИ

Лічильником називають прилад, призначений для підрахунку числа імпульсів, поданих на вхід. Вони, як і зсувні регістри, складаються з ланцюжка тригерів. Розрядність лічильника, а отже, і число тригерів, визначається максимальним числом, до якого він рахує.

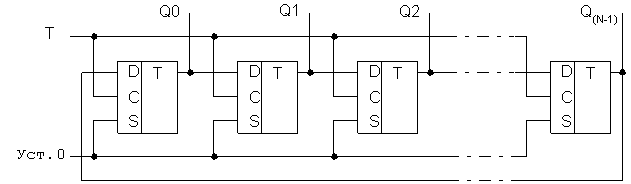

Регістр зсуву можна перетворити в кільцевий лічильник, якщо вихід останнього тригера зєднати з входом D першого. Схема такого лічильника на N розрядів наведена на рисунку 11. Перед початком підрахунку імпульсом початкової установки в нульовий розряд лічильника (Q0) записується логічна 1, в інші розряди — логічні 0. З початком рахунку кожний з лічильних імпульсів Т, що приходять, перезаписує 1 в наступний тригер, і число імпульсів, що надійшли, визначається за номером виходу, на якому є 1. Передостанній (N-1) імпульс переведе в одиничний стан останній тригер, а N-ний імпульс перенесе цей стан на вихід нульового тригера, і підрахунок розпочнеться спочатку. Таким чином, можна побудувати кільцевий лічильник з довільним коефіцієнтом перерахунку (будь-якою основою числення), змінюючи лише число тригерів в ланцюжку.

Рисунок 11 - Кільцевий лічильник на регістрі зсуву

Недолік такого лічильника - велике число тригерів, необхідних для його побудови. Більш економічні, а тому і більш розповсюджені лічильники, які побудовані на лічильних Т-тригерах. Після кожного тактового імпульсу Т сигнал на вході D змінюється на протилежний і тому частота вихідних імпульсів вдвічі менша частоти імпульсів, що надходять. Зібравши послідовний ланцюжок з n лічильних тригерів (зєднуючи вихід попереднього тригера із входом С наступного), ми отримаємо частоту ![]() . При цьому кожний вхідний імпульс змінює код числа на виході лічильника на 1 в інтервалі від 0 до

. При цьому кожний вхідний імпульс змінює код числа на виході лічильника на 1 в інтервалі від 0 до ![]() .

.

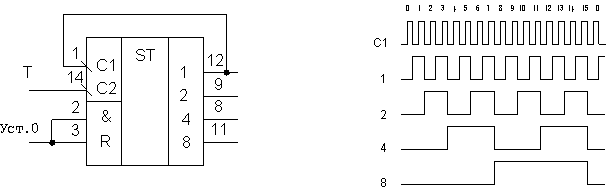

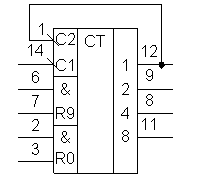

Мікросхема К555ИЕ5 (рисунок 12) містить лічильний тригер (вхід С1) і подільник на вісім (вхід С2), створений трьома зєднаними послідовно тригерами. Тригери спрацьовують по зрізу вхідного імпульсу (по переходу з 1 в 0). Якщо зєднати послідовно всі чотири тригери, то одержимо лічильник за модулем 24 =16. Максимальне число, що зберігається в лічильнику при повному заповненні його одиницями дорівнює N=24 -1=15=(1111)2 . Такий лічильник працює з коефіцієнтом рахунку К (модулем), кратним цілій степені 2, і в ньому відбувається циклічний перебір К=2n стійких станів. Лічильник має входи примусової установки в 0.

Рисунок 12 - Лічильник з коефіцієнтом перерахування 16 і його часова діаграма

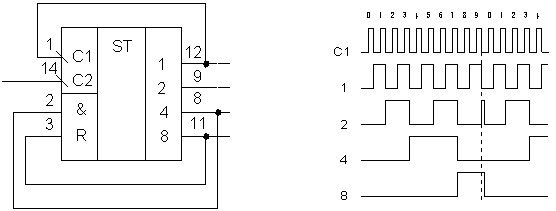

Часто потрібні лічильники з числом стійких станів, відмінним від 2n . Наприклад, в електронних годинниках є мікросхеми з коефіцієнтом рахунку 6 (десятки хвилин), 10 (одиниці хвилин), 7 (дні тижня), 24 (години). Для побудови лічильника з модулем К 2n можна використати прилад з n тригерів, для якого виконується умова 2n K. Очевидно, такий лічильник може мати зайві стійкі стани (2n -К). Виключити ці непотрібні стани можна використанням зворотних звязків, по колах яких лічильник перемикається в нульовий стан в тому такті роботи, коли він дораховує до числа К.

Для лічильника з К=10 потрібні чотири тригери (бо 23 1024 ). Лічильник повинен мати десять стійких станів N=0, 1, ..., 8, 9. В тому такті, в якому він повинен був би перейти в одинадцятий стійкий стан (N=10), його необхідно перевести в вихідний нульовий стан. Для такого лічильника можна використати мікросхему К555ИЕ5 (рисунок 13), ввівши коло зворотного звязку з виходу лічильника, відповідних числу 10 (тобто 2 і 8), на входи установки лічильника в 0 (вхід R). В самому початку 11-го стану (число 10) на обох входах елемента і мікросхеми зявляються логічні одиниці (так звана «просічка» на виході «2»), що генерує сигнал переводу всіх тригерів лічильника в нульовий стан.

Рисунок 13 - Двійково-десятковий лічильник і часова діаграма його роботи

В усіх серіях цифрових мікросхем є лічильники з внутрішньою організацією найбільш «ходових» коефіцієнтів перерахування, наприклад в мікросхемах К555ИЕ2 і К555ИЕ6 К=10, в мікросхемі К555ИЕ4 К=2б=12.

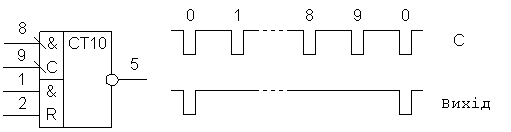

Як видно з схем і діаграм (рисунки 11-13), лічильники можуть виконувати функції подільників частоти, тобто приладів, що формують з імпульсної послідовності з частотою fвх імпульсну послідовність, на виході останнього тригера, з частотою fвих , в К разів меншу за вхідну. При такому використанні лічильників немає необхідності знати, яке число в ньому записане в поточний момент, тому подільники в деяких випадках можуть бути значно простіші за лічильники. Наприклад, мікросхема К555ИЕ1 - це подільник на 10, а К555ИЕ8 - подільник із змінним коефіцієнтом ділення К=64/n, де n=1....63.

Крім розглянутих лічильників, що підсумовують, широко застосовують реверсивні лічильники на мікросхемах К555ИЕ6, К555ИЕ7, у яких в залежності від режиму роботи вміст лічильника або збільшується на одиницю (режим додавання), або зменшується на одиницю (режим віднімання) після приходу чергового лічильного імпульсу.

Мікросхема К555ИЕ1 (рисунок 14) - подільник на 10. Установка її тригерів в 0 здійснюється одночасною подачею високого рівня на входи 1 і 2 (елемент І). Лічильні імпульси подають на вхід 8 або 9 (при цьому на іншому вході повинен бути високий рівень), або водночас на обидва входи (елемент і).

Рисунок 14 - Подільник частоти

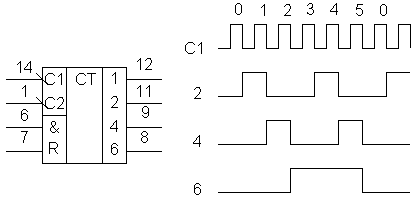

У склад мікросхеми К555ИЕ2 (рисунок 15) входять тригер з лічильним входом (вхід С1) і подільник на 5 (вхід С2). При з‘єднанні виходу лічильного тригера із входом С2 утвориться двійково-десятковий лічильник (діаграма його роботи аналогічна діаграмі на рисунку 13). Підрахунок відбувається по зрізу імпульсу. Лічильник має входи установки в 0 (R0 з логікою І) і входи установки в 9 (R9 з логікою І).

Рисунок 15 - Двійково-десятковий лічильник

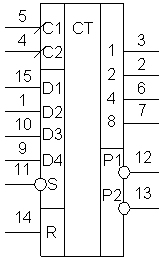

В мікросхему К555ИЕ4 (рисунок 16) входять лічильний тригер і подільник на 6.

Рисунок 16 - Лічильник на мікросхемі К555ИЕ4 та часова діаграма його роботи

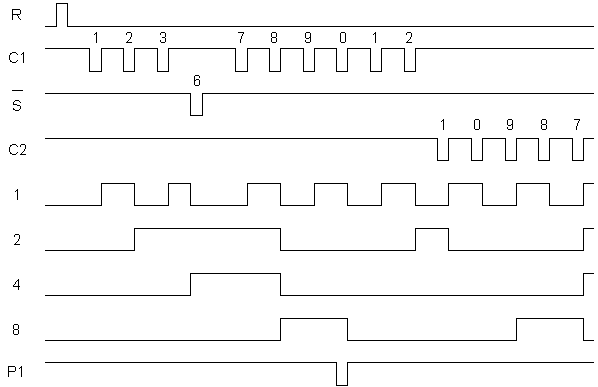

Мікросхеми К555ИЕ6 і К555ИЕ7 - реверсивні лічильники з попереднім записом; перший із них - двійково-десятковий, другий - чотирирозрядний двійковий. Установка їх в 0 відбувається при високому рівні на вході R. В лічильник можна записати число, двійковий код якого поданий на входи D1-D4 (в К555ИЕ6 від 0 до 9, в К555ИЕ7 від 0 до 15). Для цього на вхід S необхідно подати низький рівень (на входах С1 і С2 - високий рівень, на вході R - низький). Рахування почнеться із записаного числа по імпульсах низького рівня, що подаються на вхід С1 (в режимі додавання) або С2 (в режимі віднімання). інформація на виході змінюється по фронту лічильного імпульсу. При цьому на другому лічильному вході і вході S повинен бути високий рівень, на вході R - низький, а стан входів D байдужий. Водночас з кожним десятим (шістнадцятим) на вході С1 імпульсом на виході Р1 зявляється вихідний імпульс, який його повторює, що може подаватися на вхід наступного лічильника. В режимі віднімання водночас з кожним імпульсом на вході С2, що переводить лічильник в стан 9 (15), на виході Р2 зявляється вихідний імпульс. Часова діаграма роботи лічильника наведена на рис. 18. На діаграмі в режимі паралельного запису (S=0) було записане число 6 (високий рівень на входах D2 і D3).

Рисунок 17 - Реверсивний лічильник

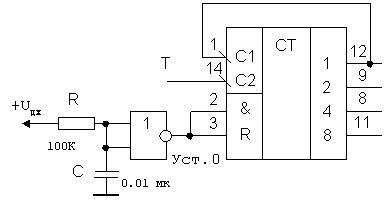

Для правильної роботи цих і всіх інших лічильників, виконаних за КМОН- технологією (серії К164, К176, К564, К561), необхідно після ввімкнення живлення (або після зниження напруги джерела живлення до 3 В) встановлювати їх у вихідний нульовий стан подачею імпульсу високого рівня на вхід R. В протилежному випадку лічильники можуть працювати із випадковими коефіцієнтами перерахування. імпульс скиду після ввімкнення живлення може подаватися автоматично, якщо ввести часозадаюче RC-коло та інвертор (рисунок 19).

Рисунок 18 - Часова діаграма роботи лічильників К555ИЕ6, К555ИЕ7

Рисунок 19 - Схема скиду лічильника в 0

Мікросхеми К176ИЕЗ і К176ИЕ4 (рисунок 1.20) є лічильниками за модулем 6 і 10 з дешифратором, працюючим на семисегментний індикатор. Їхні корпуси однакові, тільки на місці виходу 2 і 6 (виводи 3 і 2) лічильника К176ИЕЗ у десяткового лічильника К176ИЕ4 вихід 4 і 10. Лічильні імпульси подаються на вхід Т. Напруга на виході може бути як в прямому (при С=0), так і в зворотному (при С=1) коді, що дозволяє під’єднати до лічильника індикатори із спільним катодом або спільним анодом. Лічильники можна використовувати спільно з рідиннокристалічними індикаторами. У цьому випадку на вхід С подають меандр з частотою f50 Гц. При послідовному з‘єднанні лічильників сигнал знімається з виходу 6 (К176ИЕЗ) або 10 (К176ИЕ4).

Рисунок 20 - Лічильник за модулем 6 (10) з дешифратором та часові діаграми його роботи

5 ПЕРЕТВОРЮВАЧІ КОДІВ

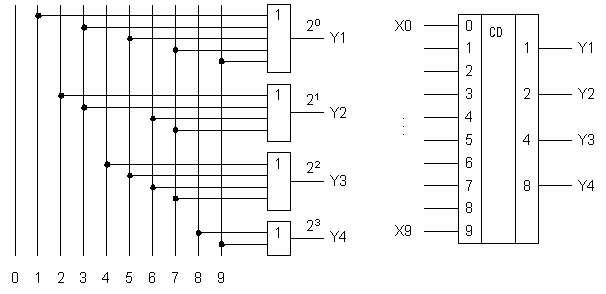

Перетворювачі кодів служать для переведення однієї форми числа в іншу. х вхідні і вихідні змінні однозначно звязані між собою. Цей звязок можна задати таблицями перемикань або логічними функціями. Розглянемо найбільш розповсюджені в практиці види перетворювачів кодів. Шифратор (кодер) перетворює сигнал в n-розрядний двійковий код. Найбільше застосування він знаходить в приладах введення інформації (пультах управління) для перетворення десяткових чисел в двійкову систему числення. Припустимо, на пульті десять клавіш з гравіюванням від 0 до 9. При натиску будь-якої з них на вхід шифратора подається одиничний сигнал (Х0-Х9). На виході шифратора повинен зявитися двійковий код (Yl, Y2, ...) цього десяткового числа. Як видно з таблиці перемикань (таблиця 3), в цьому випадку потрібен перетворювач з десятьма входами і чотирма виходами.

Таблиця 3 - Таблиця перемикань шифратора

| Десяткове число |

Двійковий код |

Десяткове число |

Двійковий код |

||||||

| Y8 |

Y4 |

Y2 |

Y1 |

Y8 |

Y4 |

Y2 |

Y1 |

||

| 0 1 2 3 4 |

0 0 0 0 0 |

0 0 0 0 1 |

0 0 1 1 0 |

0 1 0 1 0 |

5 6 7 8 9 |

0 0 0 1 1 |

1 1 1 0 0 |

0 1 1 0 0 |

1 0 1 0 1 |

На виході Y1 одиниця зявляється при натиску будь-якої непарної клавіші X1, ХЗ, Х5, Х7, Х9, тобто Y1=X1 ![]() X3

X3![]() X5

X5![]() X7

X7![]() X9. Отже, для шифратора знадобляться чотири елементи АБО: п’ятивходовий, два чотиривходових і двовходовий (рисунок 21). Y2=X2

X9. Отже, для шифратора знадобляться чотири елементи АБО: п’ятивходовий, два чотиривходових і двовходовий (рисунок 21). Y2=X2![]() X3

X3![]() X6

X6![]() X7; Y4=X4

X7; Y4=X4![]() X5

X5![]() X6

X6![]() X7; Y8=X8

X7; Y8=X8![]() X9. Отже, для шифратора знадобляться чотири елементи АБО: п’ятивходовий, два чотиривходових і двовходовий (рисунок 21).

X9. Отже, для шифратора знадобляться чотири елементи АБО: п’ятивходовий, два чотиривходових і двовходовий (рисунок 21).

Рисунок 21 - Схема шифратора на елементах АБО і його умовне графічне позначення

Дешифратор (декодер) перетворює код, що надходить на його входи, в сигнал тільки на одному з його виходів. Дешифратори широко застосовуються в приладах управління, в системах цифрової індикації з газорозрядними індикаторами, для побудови розподільників імпульсів по різних колах тощо.

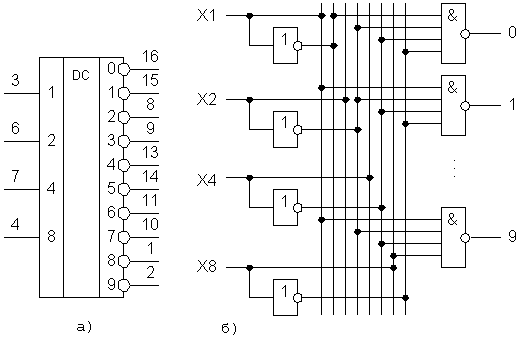

Умовне позначення дешифратора на мікросхемі К555ИД1 з десятьма виходами для дешифрування одного розряду двійково-десяткового коду 8421 і частина його принципової схеми наведені на рисунку 22. Будь-якому вхідному двійковому коду відповідає низький рівень тільки на одному виході, а на всіх інших зберігається високий рівень.

Рисунок 22 - Дешифратор на мікросхемі К555ИД1: а) умовне графічне позначення; б) принципова схема

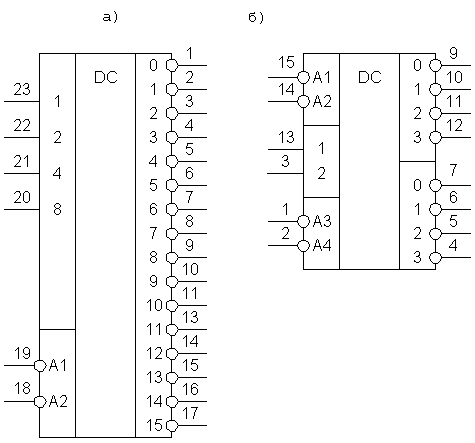

Дешифратори входять в усі серії мікросхем ТТЛ і КМОН. Наприклад, дешифратор К555ИД4 (два дешифратори в корпусі, рисунок 23, б) перетворює двійковий код в код «1 з 4», К555ИД1 і К176ИД1 в код «1 з 10», К555ИДЗ (рисунок 23, а) - в код «1 з 16».

Рисунок 23 - Приклади дешифраторів

Дешифратор на мікросхемі К555ИД1 призначений для роботи з декадними газорозрядними індикаторами. Його вихід під’єднують безпосередньо до катодів (які мають форму десяткових цифр) газорозрядного індикатора, анод якого через резистор під’єднаний до джерела живлення напругою 200-250 В. Вихідні сигнали цієї мікросхеми відрізняються від ТТЛ рівня і тому для під’єднання до неї інших мікросхем потрібно застосовувати додаткові прилади узгодження.

Мікросхема К555ИД4 складається з двох дешифраторів на 4 з обєднаними адресними входами (виводи 3 і 13) і роздільними входами стробування. Стробуванням називається виділення сигналу в певний момент часу. У даному випадку - це поява вихідного сигналу в моменти, коли на входах стробування є сигнал дозволу. Якщо на обох входах А1 і А2 будуть низькі рівні, то на виході верхнього за схемою дешифратора, номер якого відповідає еквіваленту вхідного коду, буде також низький рівень. Для нижнього (за схемою) дешифратора необхідно виконання умов: А3=1 і А4=0.

Дешифратор на мікросхемі К555ИДЗ має чотири входи для прийому чисел в коді 8421 і 16 виходів. Два входи стробування (для передачі сигналу на А1 і А2 необхідно подати низькі рівні) дозволяють обєднати мікросхеми для одержання дешифраторів на 32 виходи (рисунок 24), 64 виходи (потрібно чотири мікросхеми).

Рисунок 24 - Дешифратор на 32 виходи

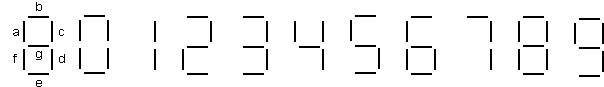

Перетворювач двійково-десяткового коду в код семисег-ментного індикатора. Числа на табло і пультах висвічуються, як правило, в десятковому коді. Для цього можна використати дешифратор на мікросхемі К555ИД1 разом з газорозрядним індикатором. Однак застосування таких індикаторів в практиці небажано через необхідність використання джерела живлення високої напруги (200 В). Зараз широке розповсюдження отримали так звані семисегментні світлодіодні і рідиннокристалічні індикатори, що працюють при тих же напругах, що і мікросхеми. В них індикація здійснюється за допомогою семи елементів (рисунок 25). Подаючи керуючу напругу на окремі елементи індикатора і викликаючи його світіння (світлодіодні індикатори) або змінюючи його забарвлення (рідиннокристалічні індикатори), можна отримати зображення десяткових цифр 0, 1, ..., 9. Деякі мікросхеми - перетворювачі коду 8421 в семисегментний показані на рисунок 26.

Рисунок 25 - Стилізоване зображення цифр в семисегментних індикаторах

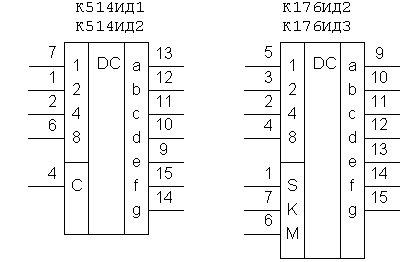

Рисунок 26 - Перетворювачі двійково-десяткового коду в семисегментний

На мікросхеми серії К514 подають вхідні сигнали рівня ТТЛ. Сигнал С служить для гасіння індикації (напругою низького рівня). При нормальній роботі рівень сигналу С=1. Дешифратор на мікросхемі К514ИД1 працює зі світлодіодними індикаторами, які мають роздільні аноди, а на К514ИД2 - з роздільними катодами. Дешифратор К514ИД2 під’єднують до індикаторів через струмообмежувальні резистори (200 - 500 Ом), а перший має такі резистори у своєму корпусі.

Мікросхеми К176ИД2 і К176ИДЗ є перетворювачами коду з вхідним регістром памяті. Запис інформації в память відбувається по фронту тактового сигналу, що подається на вхід S (при цьому сигнал на вході К=0). Якщо сигнал К=1, дешифратор блокується. Вихідний код цих дешифраторів - прямий при М=0 і зворотний при М=1. Дешифратори призначені для роботи з рідиннокристалічними і люмінесцентними індикаторами. Вони можуть працювати і зі світлодіодними індикаторами при напрузі джерела живлення 9-12 В з зниженою яскравістю світіння (через обмеження струму до 2-3 мА).

В практциці проектування різних цифрових систем часто виникає ситуація, при якій на один вихід якого-небудь пристрою треба подавати сигнали від різних джерел інформації. Таку задачу виконують пристрої, які називаються мультиплексорами.

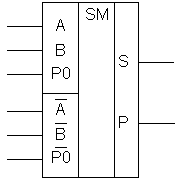

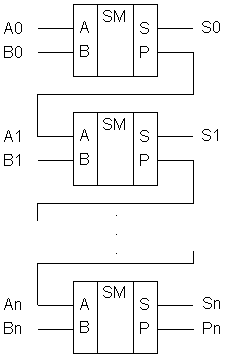

Мультиплексором називають пристрій, який здійснює підключення (комутацію) одного з N входів даних до одного виходу.

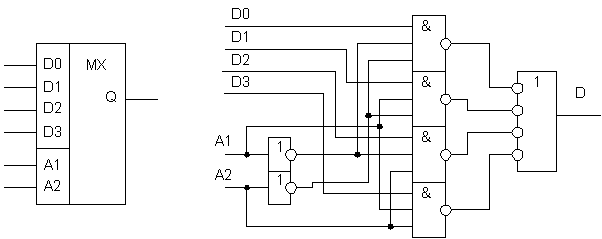

Умовне позначення мультиплексора з чотирма інформаційними входами і його принципова схема показані на рисунку 27. На вихід Q такого приладу передається логічний рівень того інформаційного входу Di , номер якого i в двійковому коді заданий на адресних входах Аl, А2. Із принципової схеми випливає, що

![]() .

.

Число інформаційних входів може бути збільшене, але при цьому доведеться збільшити і розрядність адреси.

В інтегральному виконанні випускаються мультиплексори на два входи (чотири елемента в одному корпусі), на чотири входи (два в одному корпусі), на вісім і шістнадцять входів (деякі з них показані на рисунку 28). Всі вони мають вхід дозволу вибірки V (напругою низького рівня). Мікросхема К561ЛС2 містить чотири елементи, кожний з яких реалізує функцію ![]() . Для перетворення в двоканальний комутатор її доповнюють інвертором.

. Для перетворення в двоканальний комутатор її доповнюють інвертором.

Мультиплексор в різних літературних джерелах має і інші назви: електронний комутатор, селектор. Схему мультиплексора називають селектором (від select - вибирати).

Рисунок 27 - Умовне позначення і принципова схема мультиплексора з чотирма інформаційними входами

Рисунок 28 - Умовні графічні позначення мультиплексорів

Рисунок 28 - Умовні графічні позначення мультиплексорів

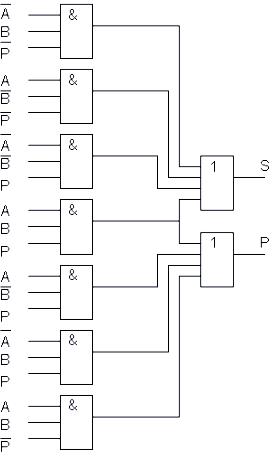

6 СУМАТОРИ

Суматор призначений для арифметичного додавання двох чисел. З принципу додавання багаторозрядних двійкових чисел випливає, що в кожному i-му розряді знаходиться сума трьох чисел за модулем два (доданки Ai , Bi і число перенесення, що надійшло з молодшого розряду Pi ) і формується сигнал переносу в старший розряд Pi+1 .

Для прикладу проаналізуємо таблицю істинності однорозрядного суматора (таблиця 4) і запишемо логічні вирази для вихідних величин

За цими функціями можна побудувати суматор на елементах і і АБО (рисунок 29). Умовне зображення однорозрядного суматора наведено на рисунку 30. Для додавання двох багаторозрядних двійкових чисел використовують багаторозрядні суматори, які є найпростішим видом послідовного з‘єднання однорозрядних суматорів (рисунок 31).

Таблиця 4 - Таблиця істинності однорозрядного суматора

| Вхід |

Вихід |

|||

| Доданки |

Перенесення |

Сума |

Перенесення |

|

| А |

В |

Рі |

S |

Pi+1 |

| 0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 0 0 0 1 1 1 1 |

0 1 1 0 1 0 0 1 |

0 0 0 1 0 1 1 1 |

Рисунок 29 - Принципова схема однорозрядного суматора

Рисунок 30 - Умовне зображення однорозрядного суматора

Рисунок 31 - Схема багаторозрядного суматора

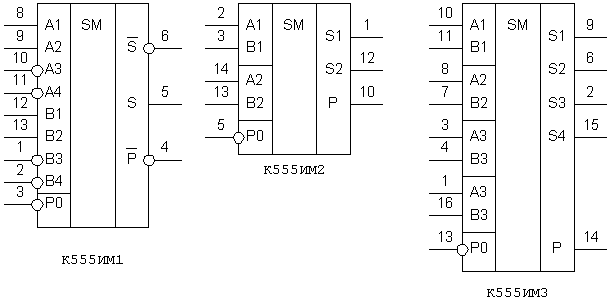

В схемах мікросхем є одно-, дво- та чотирирозрядні суматори, які можна обєднати для одержання суматорів з будь-якою розрядністю. В серію К555, наприклад, входять три суматори: однорозрядний К555ИМ1, дворозрядний К555ИМ2 та чотирирозрядний К555ИМ3 (рис. 32).

Рисунок 32 - Приклади суматорів

ПРАКТИЧНА ЧАСТИНА

Завдання

57. Логічні елементи, що застосовуються в електронно-обчислювальній техніці. Написати програму, яка моделювала б роботу мультиплексора.

1 Обґрунтування розв’язку завдання

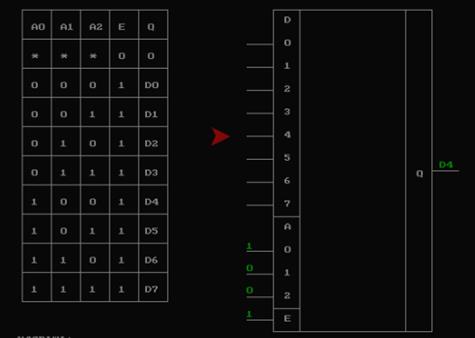

Мультиплексор передає сигнал з одного із інформаційних входів Di на єдиний вихід Q, причому номер цього входу рівний десятковому еквіваленту двійкового числа на адресних входах Ai. Вхід Е – вхід дозволу на роботу мультиплексора. Нижче наведемо таблицю істинності для мультиплексора з двома адресними входами.

A0 |

A1 |

E |

Q |

| * |

* |

0 |

0 |

| 0 |

0 |

1 |

D0 |

| 0 |

1 |

1 |

D1 |

| 1 |

0 |

1 |

D2 |

| 1 |

1 |

1 |

D3 |

![]()

В залежності від кількості інформаційних входів, які комутуються на один вихід, напишемо програму, яка демонструвала б роботу мультиплексорів з 4, 8, 16-ма інформаційними входами (мультиплексори 4-1, 8-1, 16-1). Для кожного з них програма буде креслити таблицю істинності.

2 Граф-схема алгоритму

2 Граф-схема алгоритму

3 Вказівки користувачеві

Виконувана програма selector.exe проста у виконанні, невелика за розміром, невибаглива до системи. Вона демонструє роботу мультиплексора та малює таблицю істинності. Для її роботи необхідно, щоб у каталозі, де знаходиться програма, був присутній файл egavga.bgi - графічний драйвер. Після запуску треба вибрати тип мультиплексора, після чого, користуючись клавішами управління курсором, перебираючи кодові комбінації на адресні входи, можна спостерігати проходження сигналів з інформаційних входів на вихід.

Приклад роботи програми наведений в додатку.

4 Вказівки програмісту

Текст програми написаний мовою Turbo C++. У програмі використовуються функції графічної бібліотеки. Для заповнення таблиці істинності та подачі двійкових комбінацій на адресні входи мультиплексора були використані вкладені цикли від 0 до 1 із глибиною n, де n - кількість адресних входів. В залежності від цих комбінацій за допомогою оператора switch демонструється проходження сигналу із інформаційних входів.

ВИСНОВКИ

В даній курсовій роботі були розглянуті основні логічні елементи та вузли цифрових пристроїв, їх види, визначені основні функції і значення для електронно-обчислювальної техніки. Було доведено, що вони є невід’ємними складовими обчислювальних машин, так як жодна ЕОМ або цифровий прилад не можуть обійтися без них. Для демонстрації роботи одного із вузлів цифрових приладів (мультиплексора) було написано програму.

ЛІТЕРАТУРА

1. Поджаренко В.О., Кучерук В.Ю., Марущак В.Ю. Основи цифрової техніки. – Вінниця:, ВДТУ, 2000р.

2. Хаімзон І. Я. Техніка передачі інформації. Функціональні вузли та схеми. Частина ІІ. – Вінниця:, ВДТУ,2000.- 112 с.

Додаток А

Текст програми selector . cpp

#include iostream.h

#include conio.h

#include graphics.h

#include math.h

//вибір типу мультиплексора

void sub_intro()

{

setcolor(3);

settextstyle(0,HORIZ_DIR,2);

outtextxy(90,100,ПРИНЦИП РОБОТИ МУЛЬТИПЛЕКСОРА);

settextstyle(1,HORIZ_DIR,0);

setcolor(5);

outtextxy(210,150,ВИБЕРІТЬ ТИП МУЛЬТИПЛЕКСОРА:);

setcolor(15);

settextstyle(0,HORIZ_DIR,2);

outtextxy(300,200,4-1);

outtextxy(300,240,8-1);

outtextxy(300,280,16-1);

setcolor(1);

settextstyle(1,HORIZ_DIR,0);

outtextxy(460,400,курсова робота);

outtextxy(460,420,студента групи 1 ІС-05);

outtextxy(460,440,Ткачука Андрія);

settextstyle(0,HORIZ_DIR,2);

}

//вибір мультиплексора, повернення значення кількості адресних входів

int intro()

{

int n,i,key;

i=0;

n=i+2;// n-кількість адресних входів

sub_intro();

setcolor(4);

outtextxy(280,200,);

while(!kbhit())

{

key=getch();if(key==13) goto next;//вихід із функції

key=getch();

//управління клавішами курсора

switch(key)

{

case 72:cleardevice();

i--;

if(i0) i=2;

n=i+2;

sub_intro();

setcolor(4);

outtextxy(280,200+i*40,);

break;

case 80:cleardevice();

i++;

if(i2)i=0;

n=i+2;

sub_intro();

setcolor(4);

outtextxy(280,200+i*40,);

break;

}

}

next:cleardevice();

settextstyle(1,HORIZ_DIR,0);

return(n);

}

//виведення підказки користування клавішами

void instr(int x0,int y0,int n)

{

int x,y,zm;

if(n==4){x=x0+450;y=y0;zm=20;}

else {x=x0;y=y0;}

outtextxy(x,y,КЛАВІШІ:);

if(n!=4)outtextxy(x,y+20,ENTER – вибір мультиплексора );

else

{

outtextxy(x,y+20,ENTER -);

outtextxy(x,y+40,вибір мультиплексора);

}

outtextxy(x,y+40+zm,UP - вверх);

outtextxy(x,y+60+zm,DOWN - вниз);

outtextxy(x,y+80+zm,ESC - вихід);

}

//функція креслення таблиці істинності

void table(int x,int y,int n)//x,y-координати верхнього лівого кута

{ //n-кількість адресних входів

int i,L0=100/n;

setcolor(7);

for(i=0;ipow(2,n)+3;i++)

line(x,y+i*L0,x+(n+2)*L0,y+i*L0);

for(i=0;i(n+3);i++)

line(x+i*L0,y,x+i*L0,y+(pow(2,n)+2)*L0);

}

//функція заповнення таблиці істинності

void fill(int x,int y, int n)

{

int i,j,k,t,g,L0=100/n;

for(i=0;in;i++)

switch(i)

{

case 0:outtextxy(x+L0/3+i*L0,y+L0/2,A0);

outtextxy(x+L0/3+i*L0,y+1.5*L0,*);break;

case 1:outtextxy(x+L0/3+i*L0,y+L0/2,A1);

outtextxy(x+L0/3+i*L0,y+1.5*L0,*);break;

case 2:outtextxy(x+L0/3+i*L0,y+L0/2,A2);

outtextxy(x+L0/3+i*L0,y+1.5*L0,*);break;

case 3:outtextxy(x+L0/3+i*L0,y+L0/2,A3);

outtextxy(x+L0/3+i*L0,y+1.5*L0,*);break;

}

switch(n)

{

case 2:outtextxy(x+L0/3+2*L0,y+L0/2,E);

outtextxy(x+L0/3+2*L0,y+1.5*L0,0);

outtextxy(x+L0/3+3*L0,y+L0/2,Q);

outtextxy(x+L0/3+3*L0,y+1.5*L0,0);break;

case 3:outtextxy(x+L0/3+3*L0,y+L0/2,E);

outtextxy(x+L0/3+3*L0,y+1.5*L0,0);

outtextxy(x+L0/3+4*L0,y+L0/2,Q);

outtextxy(x+L0/3+4*L0,y+1.5*L0,0);break;

case 4:outtextxy(x+L0/3+4*L0,y+L0/2,E);

outtextxy(x+L0/3+4*L0,y+1.5*L0,0);

outtextxy(x+L0/3+5*L0,y+L0/2,Q);

outtextxy(x+L0/3+5*L0,y+1.5*L0,0);break;

}

t=2;

switch(n)//заповнення таблиці кодовими комбінаціями

{

case 2://для мультиплексора з 2-ма адресними входами

for(i=0;i2;i++)

for(j=0;j2;j++)

{

switch(i)

{

case 0:outtextxy(x+L0/3,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3,y+t*L0+L0/2,1);

}

switch(j)

{

case 0:outtextxy(x+L0/3+L0,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3+L0,y+t*L0+L0/2,1);

}

outtextxy(x+L0/3+2*L0,y+t*L0+L0/2,1);

t++;

}

break;

case 3://з 3-ма адр. входами

for(i=0;i2;i++)

for(j=0;j2;j++)

for(k=0;k2;k++)

{

switch(i)

{

case 0:outtextxy(x+L0/3,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3,y+t*L0+L0/2,1);

}

switch(j)

{

case 0:outtextxy(x+L0/3+L0,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3+L0,y+t*L0+L0/2,1);

}

switch(k)

{

case 0:outtextxy(x+L0/3+2*L0,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3+2*L0,y+t*L0+L0/2,1);

}

outtextxy(x+L0/3+3*L0,y+t*L0+L0/2,1);

t++;

}

break;

case 4: //з 4-ма адр. входами

for(i=0;i2;i++)

for(j=0;j2;j++)

for(k=0;k2;k++)

for(g=0;g2;g++)

{

switch(i)

{

case 0:outtextxy(x+L0/3,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3,y+t*L0+L0/2,1);

}

switch(j)

{

case 0:outtextxy(x+L0/3+L0,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3+L0,y+t*L0+L0/2,1);

}

switch(k)

{

case 0:outtextxy(x+L0/3+2*L0,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3+2*L0,y+t*L0+L0/2,1);

}

switch(g)

{

case 0:outtextxy(x+L0/3+3*L0,y+t*L0+L0/2,0);break;

case 1:outtextxy(x+L0/3+3*L0,y+t*L0+L0/2,1);

}

outtextxy(x+L0/3+4*L0,y+t*L0+L0/2,1);

t++;

}

}

for(i=2;i(pow(2,n)+2);i++)

switch(i)

{

case 2:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D0);break;

case 3:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D1);break;

case 4:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D2);break;

case 5:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D3);break;

case 6:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D4);break;

case 7:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D5);break;

case 8:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D6);break;

case 9:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D7);break;

case 10:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D8);break;

case 11:outtextxy(x+L0/4+(n+1)*L0,y+i*L0+L0/2,D9);break;

case 12:outtextxy(x+L0/10+(n+1)*L0,y+i*L0+L0/2,D10);break;

case 13:outtextxy(x+L0/10+(n+1)*L0,y+i*L0+L0/2,D11);break;

case 14:outtextxy(x+L0/10+(n+1)*L0,y+i*L0+L0/2,D12);break;

case 15:outtextxy(x+L0/10+(n+1)*L0,y+i*L0+L0/2,D13);break;

case 16:outtextxy(x+L0/10+(n+1)*L0,y+i*L0+L0/2,D14);break;

case 17:outtextxy(x+L0/10+(n+1)*L0,y+i*L0+L0/2,D15);break;

}

}

//креслення мультиплексора

void mult(int x,int y,int n)//x,y-координати верхнього лівого кута

{ //кіль-сть адресних входів

int i,w=90/n,L0=80/n;

setcolor(7);

line(x,y,x,y+L0*(3+n+pow(2,n)));

line(x+w,y,x+w,y+L0*(3+n+pow(2,n)));

line(x+5*w,y,x+5*w,y+L0*(3+n+pow(2,n)));

line(x+6*w,y,x+6*w,y+L0*(3+n+pow(2,n)));

line(x,y,x+6*w,y);

line(x,y+L0*(3+n+pow(2,n)),x+6*w,y+L0*(3+n+pow(2,n))); line(x,y+L0*(1+pow(2,n)),x+w,y+L0*(1+pow(2,n)));

line(x,y+L0*(2+n+pow(2,n)),x+w,y+L0*(2+n+pow(2,n)));

outtextxy(x+L0/2,y+L0/3,D);

outtextxy(x+L0/2,y+(1+pow(2,n))*L0+L0/3,A);

outtextxy(x+L0/2,y+(2+n+pow(2,n))*L0+L0/3,E);

line(x-w,y+(2+n+pow(2,n))*L0+L0/2,x,y+(2+n+pow(2,n))*L0+L0/2);

outtextxy(x+5*w+L0/2,y+L0*(3+n+pow(2,n))/2,Q);

line(x+6*w,y+L0*(3+n+pow(2,n))/2,x+7*w,y+L0*(3+n+pow(2,n))/2);

for(i=0;in;i++)

//креслення та нумерація адресних входів

switch(i)

{

case 0:outtextxy(x+L0/2,y+(1+pow(2,n))*L0+L0+L0/3,0);

line(x-w,y+(1+pow(2,n))*L0+L0+L0/2,x,y+(1+pow(2,n))*L0+L0+L0/2);

break;

case 1:outtextxy(x+L0/2,y+(1+pow(2,n))*L0+2*L0+L0/3,1);

line(x-w,y+(1+pow(2,n))*L0+2*L0+L0/2,x,y+(1+pow(2,n))*L0+2*L0+L0/2);

break;

case 2:outtextxy(x+L0/2,y+(1+pow(2,n))*L0+3*L0+L0/3,2);

line(x-w,y+(1+pow(2,n))*L0+3*L0+L0/2,x,y+(1+pow(2,n))*L0+3*L0+L0/2);

break;

case 3:outtextxy(x+L0/2,y+(1+pow(2,n))*L0+4*L0+L0/3,3);

line(x-w,y+(1+pow(2,n))*L0+4*L0+L0/2,x,y+(1+pow(2,n))*L0+4*L0+L0/2);

break;

}

for(i=0;ipow(2,n);i++)

//нумерація інформаційних входів

switch(i)

{

case 0:outtextxy(x+L0/2,y+L0/3+L0,0);

line(x-w,y+L0/2+L0,x,y+L0/2+L0);break;

case 1:outtextxy(x+L0/2,y+L0/3+2*L0,1);

line(x-w,y+L0/2+2*L0,x,y+L0/2+2*L0);break;

case 2:outtextxy(x+L0/2,y+L0/3+3*L0,2);

line(x-w,y+L0/2+3*L0,x,y+L0/2+3*L0);break;

case 3:outtextxy(x+L0/2,y+L0/3+4*L0,3);

line(x-w,y+L0/2+4*L0,x,y+L0/2+4*L0);break;

case 4:outtextxy(x+L0/2,y+L0/3+5*L0,4);

line(x-w,y+L0/2+5*L0,x,y+L0/2+5*L0);break;

case 5:outtextxy(x+L0/2,y+L0/3+6*L0,5);

line(x-w,y+L0/2+6*L0,x,y+L0/2+6*L0);break;

case 6:outtextxy(x+L0/2,y+L0/3+7*L0,6);

line(x-w,y+L0/2+7*L0,x,y+L0/2+7*L0);break;

case 7:outtextxy(x+L0/2,y+L0/3+8*L0,7);

line(x-w,y+L0/2+8*L0,x,y+L0/2+8*L0);break;

case 8:outtextxy(x+L0/2,y+L0/3+9*L0,8);

line(x-w,y+L0/2+9*L0,x,y+L0/2+9*L0);break;

case 9:outtextxy(x+L0/2,y+L0/3+10*L0,9);

line(x-w,y+L0/2+10*L0,x,y+L0/2+10*L0);break;

case 10:outtextxy(x+L0/5,y+L0/3+11*L0,10);

line(x-w,y+L0/2+11*L0,x,y+L0/2+11*L0);break;

case 11:outtextxy(x+L0/5,y+L0/3+12*L0,11);

line(x-w,y+L0/2+12*L0,x,y+L0/2+12*L0);break;

case 12:outtextxy(x+L0/5,y+L0/3+13*L0,12);

line(x-w,y+L0/2+13*L0,x,y+L0/2+13*L0);break;

case 13:outtextxy(x+L0/5,y+L0/3+14*L0,13);

line(x-w,y+L0/2+14*L0,x,y+L0/2+14*L0);break;

case 14:outtextxy(x+L0/5,y+L0/3+15*L0,14);

line(x-w,y+L0/2+15*L0,x,y+L0/2+15*L0);break;

case 15:outtextxy(x+L0/5,y+L0/3+16*L0,15);

line(x-w,y+L0/2+16*L0,x,y+L0/2+16*L0);break;

}

}

//функція, що малює стрілку

void arrow(int x, int y)

{

setfillstyle(1,4);

setcolor(4);

line(x,y,x-20,y-10);

line(x,y,x-20,y+10);

line(x-15,y,x-20,y-10);

line(x-15,y,x-20,y+10);

floodfill(x-5,y,4);

}

//введення кодової комбінації на адресні входи мультиплексора

void adress(int x,int y,int n,int m)

{

int i,j,k,g,t,L0=100/n;

t=0;

switch(n)

{

case 2://для мультиплексора з 2-ма адр. входами

for(i=0;i2;i++)

for(j=0;j2;j++)

{

switch(i)

{

case 0:if(t==m)outtextxy(x-90/n,y+(1+pow(2,n))*L0,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+(1+pow(2,n))*L0,1);

}

switch(j)

{

case 0:if(t==m)outtextxy(x-90/n,y+(2+pow(2,n))*L0-L0/5,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+(2+pow(2,n))*L0-L0/5,1);

}

outtextxy(x-90/n,y+(3+pow(2,n))*L0-L0/2.5,1);

t++;

}

break;

case 3:// для мультиплексора з 3-ма адр. входами

for(i=0;i2;i++)

for(j=0;j2;j++)

for(k=0;k2;k++)

{

switch(i)

{

case 0:if(t==m)outtextxy(x-90/n,y+pow(2,n)*L0,0);break;

case 1:if(t==m)outtextxy(x-90/n,y+pow(2,n)*L0,1);

}

switch(j)

{

case 0:if(t==m)outtextxy(x-90/n,y+pow(2,n)*L0+L0-L0/4,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+pow(2,n)*L0+L0-L0/4,1);

}

switch(k)

{

case 0:if(t==m)outtextxy(x-90/n,y+pow(2,n)*L0+2*L0-L0/2,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+pow(2,n)*L0+2*L0-L0/2,1);

}

outtextxy(x-90/n,y+pow(2,n)*L0+3*L0-L0/1.5,1);

t++;

}

break;

case 4:// для мультиплексора з 4-ма адр. входами

for(i=0;i2;i++)

for(j=0;j2;j++)

for(k=0;k2;k++)

for(g=0;g2;g++)

{

switch(i)

{

case 0:if(t==m)outtextxy(x-90/n,y+(pow(2,n)-2)*L0+L0/3,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+(pow(2,n)-2)*L0+L0/3,1);

}

switch(j)

{

case 0:if(t==m)outtextxy(x-90/n,y+(pow(2,n)-1)*L0+L0/6,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+(pow(2,n)-1)*L0+L0/6,1);

}

switch(k)

{

case 0:if(t==m)outtextxy(x-90/n,y+(pow(2,n))*L0,0);break;

case 1:if(t==m)outtextxy(x-90/n,y+(pow(2,n))*L0,1);

}

switch(g)

{

case 0:if(t==m)outtextxy(x-90/n,y+(pow(2,n)+1)*L0-L0/4,0);

break;

case 1:if(t==m)outtextxy(x-90/n,y+(pow(2,n)+1)*L0-L0/4,1);

}

outtextxy(x-90/n,y+(pow(2,n)+2)*L0-L0/2.5,1);

t++;

}

}

}

void main()

{

int dr=DETECT,mod,y,i,n,L0,key,c;

initgraph(dr,mod,);

again:;

n=intro();

table(25,10,n);

fill(25,10,n);

mult(310,10,n);

instr(20,380,n);

i=-1;

y=0;

L0=80/n;

setcolor(2);

//на адр. входи не подаються сигнали

if(n==2)outtextxy(310-90/n,75+(3+pow(2,n))*L0-L0/2.5,0);

if(n==3)outtextxy(310-90/n,82+pow(2,n)*L0+3*L0-L0/1.5,0);

if(n==4)outtextxy(310-90/n,95+n+(pow(2,n)+2)*L0-L0/2.5,0);

outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,0);

//на адр. входи подаються сигнали

while(!kbhit())

{

key=getch();if(key==13){cleardevice();goto again;}

if(key==27) goto next;

key=getch();

//керування стрілкою

switch(key)

{

case 72:cleardevice();//стрілка вверх

table(25,10,n);

fill(25,10,n);

mult(310,10,n);

instr(20,380,n);

i--;

if(i0) i=pow(2,n)-1;

arrow(260,10+(i+1)*L0+L0/2);//y+L0/2+7*L0

setcolor(2);

//комутація з одного із інф. входів на вихід

switch(i)

{

case 0:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D0);

break;

case 1:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D1);

break;

case 2:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D2);

break;

case 3:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D3);

break;

case 4:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D4);

break;

case 5:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D5);

break;

case 6:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D6);

break;

case 7:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D7);

break;

case 8:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D8);

break;

case 9:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D9);

break;

case 10:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D10);

break;

case 11:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D11);

break;

case 12:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D12);

break;

case 13:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D13);

break;

case 14:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D14);

break;

case 15:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D15);

break;

}

adress(310,10,n,i);

break;

case 80:cleardevice();//стрілка вниз

table(25,10,n);

fill(25,10,n);

mult(310,10,n);

instr(20,380,n);

i++;

if(ipow(2,n)-1) i=0;

arrow(260,(i+1)*L0+10+L0/2);

setcolor(2);

switch(i)

{

case 0:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D0);

break;

case 1:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D1);

break;

case 2:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D2);

break;

case 3:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D3);

break;

case 4:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D4);

break;

case 5:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D5);

break;

case 6:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D6);

break;

case 7:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D7);

break;

case 8:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D8);

break;

case 9:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D9);

break;

case 10:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D10);

break;

case 11:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D11);

break;

case 12:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D12);

break;

case 13:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D13);

break;

case 14:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D14);

break;

case 15:outtextxy(310+450/n+1.5*L0,y+L0*(3+n+pow(2,n))/2,D15);

break;

}

adress(310,10,n,i);

break;

}

}

next:closegraph();

}

Результат роботи програми

Демонстрація роботи мультиплексора типу 8-1.