Многопроцессорный вычислительный комплекс

СОДЕРЖАНИЕ: Разработка структуры многопроцессорного вычислительного комплекса с многовходовым оперативным запоминающим устройством. Характеристика структурной схемы МПВК: блок генерации сигналов, блок микропроцессора, блок сопряжения, памяти и контроллеров пуска.Министерство образования республики Беларусь.

Белорусский Государственный Университет

Информатики и Радиоэлектроники

Кафедра ЭВМ

Пояснительная записка

к курсовому проекту

По курсу: «Вычислительные комплексы системы и сети»

На тему: «Многопроцессорный вычислительный комплекс»

Выполнил:

ст. гр. 650502

Курганович И.В.

Проверил:

Жеребятьев В.И.

Минск 2000г.

Задание к курсовому проекту

Разработать схему многопроцессорного вычислительного комплекса с многовходовыми ОЗУ.

Исходные данные:

тип микропроцессора – 80386;

количество микропроцессоров – 2;

объем ОЗУ – 640 кб;

объем ПЗУ – 256 кб;

количество параллельных ПУ – 2;

количество последовательных ПУ – 2.

В схеме должна быть предусмотрена возможность подключения внешних запоминающих устройств.

Содержание:

Введение

1. Разработка структурной схемы

2. Разработка функциональной схемы

3. Выбор и обоснование элементов

4. Разработка принципиальной схемы

Заключение

Литература

Введение

Вычислительная техника в своем развитии по пути повышения быстродействия ЭВМ приблизилась к физическим пределам, которые обусловлены ограниченной скоростью распространения сигналов в линиях, связывающих элементы и узлы машины. В этих условиях требования практики (сложные физико-технические расчеты, метеорологические расчеты, многомерные экономико-математические модели и другие задачи) по дальнейшему повышению быстродействия ЭВМ могут быть удовлетворены только путем распространения принципа параллелизма на сами устройства обработки информации и создания многомашинных и мультипроцессорных вычислительных систем. Такие системы позволяют производить распараллеливание во времени выполнение программы или параллельное выполнение нескольких программ (задач).

В настоящее время исключительное важное значение приобрела проблема обеспечения высокой надежности и готовности вычислительных систем, работающих в составе различных АСУ и АСУ ТП, в особенности, при работе в режиме реального времени. Эта проблема решается на основе использования принципа избыточности, который также диктует построение многопроцессорных и многомашинных систем.

Различие понятий многомашинной и мультипроцессорной системой заключается в следующем. Многомашинная вычислительная система содержит несколько ЭВМ, каждая из которых имеет свою оперативную память и работает под управлением своей операционной системы, а также средства обмена информацией между машинами. Реализация обмена информацией происходит в конечном счете за счет взаимодействия операционных систем машин между собой. Это ухудшает динамические характеристики процессов межмашинного обмена данными. Но применение многомашинных систем позволяет повысить надежность вычислительных комплексов. Однако можно заметить, что при этом оборудование комплекса недостаточно эффективно используется для этой цели. В многомашинной системе достаточно в каждой ЭВМ выйти из строя по одному устройству (даже разных типов), как вся система становится неработоспособной.

Этих недостатков лишены мультипроцессорные системы. В таких системах процессоры обретают статус рядовых агрегатов вычислительной системы, которые подобно другим агрегатам, таким как модули памяти, каналы, периферийные устройства, включаются в состав системы в нужном количестве.

Вычислительная система называется мультипроцессорной, если она содержит несколько процессоров, работающих с общей оперативной памятью и, быть может, с общими внешними запоминающими устройствами, и управляется одной общей операционной системой.

В мультипроцессорной системе достигается более быстрая, чем в многомашинных системах, реакция на ситуации, возникающие внутри системы и в ее внешней среде, и более высокая надежность и живучесть, так как система сохраняет работоспособность, пока работоспособны хотя бы по одному модулю каждого типа устройств. На основе многопроцессорности и модульного принципа построения других устройств системы возможно создание систем повышенной живучести за счет автоматической перестройки структуры (автоматической реконфигурации) при отказах в отдельных агрегатах, в том числе в процессорах. Многомашинные и многопроцессорные системы могут быть однородными и неоднородными. Однородные системы содержат однотипные ЭВМ или процессоры.

Неоднородные многомашинные системы состоят из ЭВМ различного типа, а в неоднородных мультипроцессорных системах используются различные специализированные процессоры, например, процессоры для операций с плавающей запятой, для обработки десятичных чисел, процессор, реализующий функции операционной системы и другие. Принципы организации мультипроцессорных систем сильно отличаются в зависимости от их назначения. Поэтому целесообразно подразделять их на два класса:

1.мультипроцессорные вычислительные системы, ориентированные на повышение производительности;

2.мультипроцессорные вычислительные системы, ориентированные на повышение надежности и живучести.

Существуют три типа структурной организации МПВК: с общей шиной; с перекрестной коммутацией; с многовходовым ОЗУ.

В комплексах с многовходовыми ОЗУ все , что связано с коммутацией устройств , осуществляется в ОЗУ. В этом случае модули ОЗУ имеют число входов , равное числу устройств , которые к ним подключаются, т.е. для каждого устройства предусматривается свой вход в ОЗУ. В таких комплексах очень просто решается вопрос о выделении каждому процессору своей оперативной памяти, недоступной другим процессорам. Выделение индивидуальной памяти каждому процессору позволяет хранить в ней информацию, которая необходима только одному процессору. Это позволяет избежать части конфликтов, которые неизбежно возникают при общей оперативной памяти. Кроме того, уменьшается вероятность искажения информации в ОЗУ другими процессорами.

Однако комплексы с многовходовыми ОЗУ имеют тот недостаток, что в случае выхода из строя какого-либо процессора, доступ к его памяти затруднен и информация может быть переписана в другой модуль ОЗУ только через канал ввода-вывода и внешнее запоминающее устройство, что требует много времени.

1. Разработка структурной схемы

Целью данного курсового проекта является разработка структуры многопроцессорного вычислительного комплекса с многовходовым ОЗУ.

Структурная схема такого МПВК приведена в приложении на схеме 1.

Рассмотрим блоки, представленные на данной схеме.

1. Блок генерации сигналов.

Функционирование любого вычислительного комплекса основывается на сигналах. Основные сигналы, которые присутствуют в любом компьютере это CLK и RESET. Сигнал CLK используется для синхпронизации раборы всех блоков вычислительного комплекса. Сигнал RESET используется для сброса всех блоков вычислительного комплекса или установки их в исходное состояние. Вышеописанные сигналы формируются блоком генерации сигналов.

Для формирования сигналов блок генерации сигналов должен получать информацию о работе других блоков (чем они занимаются в данный момент времени). Такая информация поступает в блок при помощи сигналов S0 и S1. После декодирования этих сигналов, блок выдает сигнал готовности READY для тех устройств, которые необходимы для выполнения поставленной задачи.

2. Блок микропроцессора.

По данным задания курсового проекта блоков микропроцессора должно быть два. Оба блока работают на одинаковой частоте, т.к. используют идентичные сигналы синхронизации. Внутренняя структура блоков и выполняемые ими функции полностью совпадают, поэтому рассмотрим только один микропроцессорный блок.

Микропроцессорный блок является главным элементом МПВК. Он организует работу всего МПВК. Для связи со всеми блоками комплекса микропроцессорный блок использует сигнал READY, который выдается блоком генерации и разрешает микропроцессорному блоку начать работу по решению следующей задачи

Для работы с передачей информации блок микропроцессора выдает сигналы: S0 и S1 для блока генерации, MEMR, MEMW, IOR, IOW для блока сопряжения. Сигнал MEMR показывает, что блоку микропроцессора необходимо прочитать данные из блока памяти и блок сопряжения должен установить связь между этими блоками. Сигнал MEMW показывает, что блоку микропроцессора необходимо занести данные в блок памяти. Сигнал IOR показывает, что блоку микропроцессора необходимо прочитать данные из периферийного устройства и блок сопряжения должен соединить микропроцессорный блок с блоком контроллеров ПУ, через который проходят данные. Сигнал IOW показывает, что блоку необходимо вывести данные на какое-то ПУ.

В блоке есть две шестнадцатиразрядные шины: шина адреса ( ADDRES[0..15] ) и шина данных ( DATA[0..15] ). Это двунаправленные шины, по которым происходит передача адресов и данных во всех направлениях.

Такие сигналы и шины присущи любому компьютеру и являются стандартными.

Для того, чтобы организовать совместную работу двух микропроцессорных блоков в курсовом проекте введен сигнал BUSY. Этот сигнал вырабатывается после анализа текущих задач, которые выполняют блоки, или задач, которые они намерены выполнять.

В многопроцессорном вычислительном комплексе необходимо отследить ситуации, когда происходит одновременное обращение к блоку памяти или когда во время работы с блоком памяти одним блоком происходит обращение к памяти от другого блока. При выявлении таких ситуаций сигналом BUSY, один из микропроцессорных блоков переводится в состояние ожидания.

3. Блок сопряжения.

Предназначен для подключения микропроцессорных блоков к блоку контроллеров периферийных устройств и к блоку памяти. В блоке сопряжения происходит выяснение к какому ПУ или к какой части модуля памяти необходимо подключиться микропроцессорному блоку и соединение его с данным устройством.

Так же в этом блоке реализован механизм отслеживания исключительных ситуаций и организации работы после них. Блок организует передачу данных и адресов по четырем независимым двунаправленным шинам. Для работы с периферийными устройствами блок получает сигнал INT, который показывает, что какому-то ПУ необходимо прервать работу микропроцессорного блока. Блок сопряжения анализирует этот сигнал и выполняет действия, необходимые для передачи прерывания.

4. Блок памяти.

По данным задания к курсовому проекту модуль памяти должен содержать ПЗУ на 256 кбайта и ОЗУ на 640 кбайт. Для обращения к ячейкам памяти используется шестнадцатиразрядная шина адреса ADDRES[0..15]. Так как 386 процессор имеет шестнадцатиразрядную шину данных, то и для работы с памятью используется шестнадцатиразрядная шина. Для работы с модулем памяти используется 4 шины, по две на каждый процессорный модуль, так как в курсовом проекте должна быть реализована многовходовая оперативная память. Через блок сопряжения данные передаются в один из процессорных модулей, либо по каналам ПДП на контроллеры ПУ.

5. Блок контроллеров ПУ.

Включает в себя контроллеры ПУ, которые могут использоваться обоими процессорными модулями.

Связь с процессорами происходит через блок сопряжения по шестнадцатиразрядной шине адреса и восьмиразрядной шине данных. Для прерывания процессоров блоком контроллеров используется сигнал INT. В зависимости от программного обеспечения процессорный блок организует либо программную передачу данных, либо каналы ПДП.

В курсовом проекте рассмотрены только ситуации, которые связаны с передачей данных из процессорных блоков в блок памяти и обратно. Связь между процессорами и контроллерами ПУ и соперничество за них может быть реализовано программно в специализированной операционной системе.

2. Разработка функциональной схемы

Функциональная схема разрабатываемого многопроцессорного комплекса приведена в приложении схема 2.

Рассмотрим структуру данного МПВК на основе блоков, приведенных в структурной схеме.

В блок генератора сигналов включены два одинаковых генератора, по одному для каждого процессора. Генераторами вырабатываются сигналы, на основе которых работает весь МПВК. Генераторы формируют сигналы синхронизирующие работу всех устройств, которые входят в комплекс, включая процессор (CLK); сигналы сброса всех устройств в исходное состояние (RESET); сигналы окончания очередного цикла шины и начала нового цикла (READY). Для генерации сигнала READY используются сигналы: S0,S1; ARDYN,SRDYN (разрешают формирование сигнала READYв соответствии с сигналами ARDY и SRDY соответственно).

Два генератора используются потому, что каждый процессор может выполнять свою функцию и свой цикл шины, так как у каждого есть своя шина.

Блок микропроцессора включает следующие устройства:

- микропроцессор с шестнадцатиразрядными шинами данных и адреса, и управляющими сигналами;

- шестнадцатиразрядный регистр адреса и шинный формирователь;

- шинный контроллер.

Процессор (кроме работы с данными) выполняет следующие функции:

- управление контроллером и формирование вместе с ним очередного цикла шины (используются сигналы S0,S1,M/IO,HLDA);

- управление работой регистра-защелки адреса (сигналы S0,S1,HLDA);

- управление передачей данных (сигнал BHE);

Процессор использует такие входные сигналы как:

- CLK , который вырабатывается синхрогенератором;

- RESET , сброс в исходное состояние;

- READY, организация нового цикла шины;

- BUSY в данном вычислительном комплексе используется в том случае, когда второй процессор работает с памятью, чтобы остановить первый процессор если ему тоже нужна память;

- INTR , прерывания процессора;

- HOLD, запрос на захват шины.

Шинный контроллер управляет работой системной шины в зависимости от того, кокой цикл нужно выполнить: чтение или запись в память, чтение или запись в порт. Контроллер также управляет передачей данных: разрешением передачи и направлением.

Регистры-защелки адреса используются для того, чтобы выдавать требуемый адрес в течении всего цикла шины.

Шинные формирователи используются для передачи данных в обоих направлениях и выдачи данных в течение всего цикла шины.

Блок сопряжения включает следующие устройства:

- две системные шины AT для обоих процессорных модулей;

- контроллер ПДП с регистром для формирования шестнадцатиразрядного адреса;

- шинные формирователи для передачи данных с системной шины на ПУ и наоборот;

- контроллер прерываний.

Две системные шины введены для увеличения быстродействия, чтобы каждый процессор мог обращаться к памяти или к ПУ в любое время.

Контроллер ПДП организует каналы ввода-вывода для передачи данных от ПУ к памяти и наоборот минуя процессор и давая ему возможность заниматься своей задачей.

Контроллер ПДП на время передачи становится “ хозяином ” системной шины. Прямой доступ к памити организуется следующим образом: Устройствами ввода-вывода на системную шину выдаются запросы DREQ, которые принимаются контроллером; контроллером формируется запрос на захват системной шины HRQ; получив сигнал HRQ процессор выдает сигнал HLDA, подтверждающий захват системной шины; контроллером формируется сигнал DACK, сообщающий устройству ввода-вывода о начале обмена данными; контроллер выдает сформированный адрес ячейки памяти, предназначенной для обмена, причем адрес выдается побайтно; формируются сигналы MEMR, MEMW и IOR, IOW, обеспечивающие управление обменом; после окончания цикла ПДП либо повторяется цикл с изменением адреса, либо прекращается обмен и управление шиной возвращается процессору.

Контроллер прерываний служит для прерывания процессора при обращении к нему какого-либо устройства.

Прерывание организуется следующим образом:

Устройство ввода-вывода может запросить обслуживание путем подачи активного сигнала на один из входов запроса IRQ0 – IRQ7 через системную шину. Если контроллер удовлетворит запрос, его вывод INTR активизируется и соответствующий сигнал поступает на вход INTR процессора. Вход INTR микропроцессора асинхронный, то есть он может принять запрос в любое время. Процессор выдает два импульса подтверждения прерывания INTA, которые сообщают контроллеру о том, что процессор воспринял его запрос на прерывание. Первый импульс INTA используется контроллером для определения источника выдачи вектора прерывания. По второму импульсу INTA контроллер помещает на шину данных байт вектора прерывания.

Блок памяти состоит из следующих устройств: регистр адреса, шинный формирователь для данных, ПЗУ, ОЗУ.

Блок контроллеров ПУ включает в свой состав два контроллера: для последовательных и параллельных периферийных устройств.

Общее функционирование комплекса ничем не отличается от работы простой ЭВМ общего назначения. Отличие в том, что после формирования сигналов MRDC или MWDC одним процессором, начинает отслеживаться ситуация, когда эти сигналы сформирует другой процессор и перевод этого процессора в состояние ожидания. После завершения работы с памятью первый процессор формирует сигнал, переводящий второй процессор из состояния ожидания в рабочий режим.

3. Выбор и обоснование элементов

Описание микропроцессора 80386:

1. Вывод – ВНЕ – выходной сигнал разрешения передачи старшего байта, активный – низкий.:

2. Выводы S 0, S 1 – выходные сигналы состояния. Вместе с М/-IO,COD/ -INTA определяют текущее состояние микропроцессора.

3. Выводы PEREQ ,– PEACK – входной и выходной сигнал соответственно. Запрос от сопроцессора и подтверждение сопроцессору. Не используется.

4. Выводы А23 – А0 – выходы на шину адреса. Разряды А23 – А16 во время обращения к портам равны нулю.

5. Выводы D 15 – D 0 – двунаправленная шина данных.

6. Вывод CLK – входной сигнал синхронизации микропроцессора, внутри делится на 2.

7. Вывод RESET – входной сигнал сброса микропроцессора. Активный– высокий. Минимальная длительность – 16 тактов системного синхросигнала.

8. Вывод M /- IO – выходной сигнал, позволяет отличить обращение к памяти от обращения к порту.

9. Вывод COD /- INTA – выходной сигнал, позволяет отличить цикл выборки команды от цикла чтения данных и цикл подтверждения прерывания от цикла чтения/записи порта.

10. Вывод – LOCK – выходной сигнал блокировки захвата шины. Активизируется по команде LOCK или в цикле подтверждения прерывания.

11. Вывод – READY – входной сигнал готовности шины. Завершает цикл шины. Активный – низкий. Игнорируется во время активного сигнала HLDA.

12. Выводы HOLD , HLDA – входной и выходной сигналы соответственно. Запрос на захват шины и подтверждение захвата.

13. Вывод INTR – входной сигнал запроса на прерывание.

14. Вывод NMI – входной сигнал немаскируемого запроса на прерывание. Циклы подтверждения прерывания не вырабатываются.

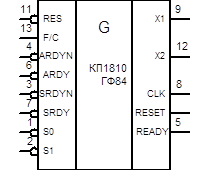

Описание синхрогенератора К1810ГФ84.

Синхрогенератор ( или генератор тактовых импульсов ) К1810ГФ84 служит для синхронизации работы процессора и других периферийных микросхем. Он также синхронизирует сигнал готовности READY при его генерации асинхронными микросхемами или схемами с иной синхронизацией. Также генерирует сигнал RESET сброса процессора при включении питания или при нажатии кнопки RESET (сброс).

|

Конструктивно микросхема выполнена по CMOS–технологии в корпусе с 18 выводами, расположенными в два ряда.

Описание выводов микросхемы: CLK – системная синхронизация, используеncz микропроцессором и другими микросхемами, работа которых должна быть синхронной с ним (частота выхода CLK равна удвоенной внутренней процессорной частоте и определяется частотой используемого кварца, а именно равна 12 МГц); F/C – выбор частоты/кристалла, определяет источник для создания синхронизирующего сигнала CLK(когда F/C=0 для генерации CLK используется внутрисхемный осциллятор, если F/C=1, то используется входной сигнал, подаваемый на вход EFI); EFI – этот вход управляет генерацией сигнала CLK, если F/C=1 (в PC/AT не используется);Х1,Х2 – через эти выводы кварц подсоединяется к внутреннему генератору для создания колебательного контура;

PCLK – это выход синхросигнала с частотой, равной половине частоты CLK (в PC/AT не используется);ARDYEN – это сигнал разрешения асинхронного входа готовности, выделяет сигнал ARDY, используемый для удлинения текущего цикла шины;ARDY – это входной асинхронный сигнал для образования выходного сигнала READY на удлинение цикла шины; SRDYEN – этот входной сигнал аналогичен ARDYEN, но только он синхронный, выбирает SRDY как источник формирования выходного сигнала READY; SRDY– это входной сигнал синхронизированной готовности, должен быть синхронизирован относительно CLK; S0,S1 – эти входы соединены с выводами S0,S1 процессора, давая синхрогенератору информацию о цикле шины;READY – это выходной сигнал готовности, который разрешает завершение текущего цикла шины;RES – это входной сигнал ‘входной сброс’, который разрешает выходной сигнал RESET синхрогенератора; RESET – это выходной сигнал, который появляется при подаче сигнала разрешения на вход RES (используется для перевода всей системы в начальное состояние);

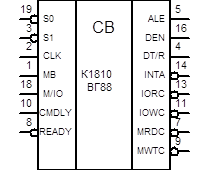

Описание шинного контроллера К1810ВГ88.

|

Шинный контроллер К1810ВГ88 предназначен для генерации сигналов, управляющих различными циклами шины: обменом данными между процессором и периферийными устройствами, а также для синхронизации этих обменов с работой процессора и других микросхем. При этом сам контроллер синхронизируется сигналом PROCCLK от КП1810ГФ84.

Конструктивно контроллер выполнен в корпусе с 20 выводами с двухрядным их расположением.

Описание выводов микросхемы: CLK – системная синхронизация, входной сигнал, идущий от синхрогенератора КП1810ГФ84; S0,S1,M/IO – это входные сигналы, с дешифрации которых контроллер начинает свою работу по выполнению совместно с процессором очередного цикла шины ( расшифровка различных комбинаций этих сигналов приведена при описании выводов процессора с теми же названиями);МВ– это входной сигнал выбора режима шины MULTIBUS;READY– сигнал на этом входе, указывает на окончание текущего цикла шины;CMDLY– этот входной сигнал позволяет задержать начало работы контроллера по выполнению очередного цикла шины; CENL– это входной сигнал, называемый разрешением защелкивания команды (в PC/AT на этот вход должна подаваться логическая единица);CEN/AEN– это входной сигнал, называемый ‘разрешение команды/разрешение адреса’;ALE – это выходной сигнал, называемый ‘разрешение защелки адреса’;DEN– это выходной сигнал разрешения передачи данных, определяет передачу данных со входов на выходы в шинных формирователях, подсоединенных к системной шине; DT/R – это выходной сигнал, определяющий направление передачи данных ( микросхема DD14 используется для передачи младшего байта данных, а DD13 – старшего байта данных);MCE – это выходной сигнал разрешения каскадирования (в PC/AT не используется); INTA – это выходной сигнал подтверждения аппаратного прерывания;IORC – это выходной сигнал управления, сообщающий периферийному устройству, что оно должно выставит данные на шину для последующего их чтения процессором;IOWC - это выходной сигнал управления, информирующий о протекании цикла шины записи данных в периферийный порт; MRDC– это выходной сигнал, сообщающий о проведении цикла шины чтения данных из ОП; MWTC– этот выходной сигнал информирует о протекании цикла шины записи данных в ОП.

Описание буферного регистра КП580ИР82.

Используется для организации запоминающих буферов, адресных защелок, портов ввода-вывода и тому подобное. Буферные регистры состоят из восьми информационных триггеров с трехстабильными выходами, общими сигналами записи информации и управления выходными схемами.

|

Назначение выводов: D7 – D0 – линии входных данных; Q7 – Q0 – линии выходных данных; C- стробирующий сигнал; CS – разрешение выдачи данных. Регистр принимает и отображает информацию синхронно с положительным перепадом тактового импульса, подаваемого на вход С. Состояния регистра приведены в таблице.

| Входы | Выход триггера | Выходы | |||

| CS | С | Dn | Q | Q0..Q7 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 1 | 1 | 1 | ||

| 1 | 0 | 0 | Z | ||

| 1 | 1 | 1 | Z | ||

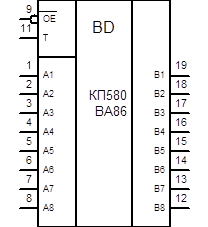

Описание шинного формирователя КП580ВА86.

Применяются как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяет использовать их для построения двунаправленных согласующих буферов межмодульной связи.

|

Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления Т и ОЕ. Функциональные блоки состоят из двух усилителей-формирователей с Z-состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу.

Назначение выводов: А7 – А0 – вход-выход линий данных. В зависимости от состояния входа Т они могут быть входными, если Т=1 и выходными, если Т=0; В7 – В0 – вход-выход линий данных. Аналогично А7 – А0.

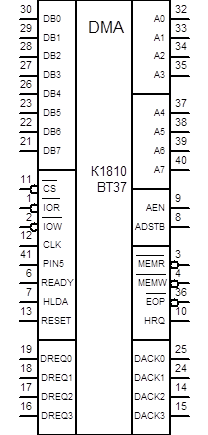

Описание контроллера ПДП К1810ВТ37.

Используется в составе МПВК для реализации прямого доступа к памяти по четырем независимым каналам с положительными или отрицательными приращениями адреса. Каждый канал может выполнять до64К циклов ПДП иимеет возможность автоматической инициализации, то есть повторения циклов ПДП с теми же параметрами.

|

Назначение выводов: CLK – вход для подключения тактового генератора; CS – выбор кристалла; RESET – сброс, переход в исходное состояние; READY – готовность; HLDA – подтверждение захвата системной шины; DREQ3 – DREQ0 – входы запросов на ПДП от внешних устройств; DB7 – DB0 – двунаправленная шина данных с буфером. В циклах ПДП на эти линии выдается восемь старших разрядов адреса, которые необходимо “ защелкнуть ” на внешнем регистре сигналом ADSTB; IOR – чтение, разрешает выдачу данных из внешних устройств; IOW – запись, разрешает запись данных в регистры внешних устройств; EOP – окончание процесса, вход-выход для указания окончания процесса передачи данных в режиме ПДП; А7 – А0 – адресные выходы; HRQ – выход запроса на захват системной шины; DACK3 – DACK0 – выходные линии подтверждения ПДП; AEN – разрешение адреса, устанавливается на время выдачи восьми разрядов адреса ОЗУ на линии DB7 –DB0; ADSTB – строб адреса, для записи старшего разряда адреса во внешний регистр; MEMR – чтение из памяти; MEMW – запись в память.

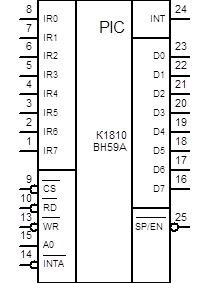

Описание контроллера прерываний К1810ВН59А.

Все запросы на аппаратные прерывания из системной шины направляются через контроллер прерываний К1810ВН59А. Этот контроллер генерирует запросы прерываний на вход INTR микропроцессора. Контроллер может принимать сигналы прерываний от нескольких устройств, назначать им приоритеты и прерывать работу процессора.

|

Описание выводов контроллера: D7 – D0 – двунаправленная шина данных; INTA – вход подтверждения прерывания, разрешающий контроллеру выдать вектор прерывания на шину данных; IRQ7 – IRQ0 – асинхронные входные сигналы запросов прерываний; INTR – выходной сигнал действительного запроса на прерывание для прерывания процессора и организации обработки возникшего прерывания; SP/EN – в PC/AT не используется; CS – вход выбора контроллера, разрешающий связь между процессором и контроллером при активных IOR или IOW; WR – вход запись, разрешающий программирование контроллера; RD – вход чтение, разрешающий считывание некоторых регистров контроллера; A0 – вход адреса, использующийся совместно с CS, WR или RD для записи/считывания внутренних регистров контроллера.

|

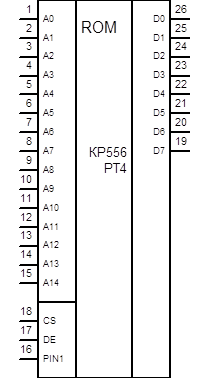

Описание микросхемы ПЗУ КР556РТ4. Микросхема имеет емкость 32 кбайта и представляет собой перегружаемую ПЗУ. Имеет 15 адресных входа и 8 выходов данных. Сигналы CS и DE для выбора данной микросхемы. Выход PIN1 для перепрограммирования не используется.

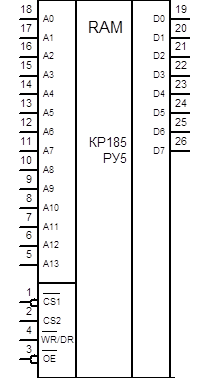

Описание микросхемы ОЗУ КР158РУ5.

Микросхема имеет емкость 256 кбайта и представляет собой оперативное запоминающее устройство. Имеет 14 адресных входа и 8 выходов данных. Сигналы CS1 и CS2 для выбора данной микросхемы. На них подается А15 с системной шины для отличия обращения к ПЗУ от ОЗУ ( для ОЗУ А15=0 ). Выход WR/RD для определения операции чтения или записи. Сигнал ОЕ не используется.

|

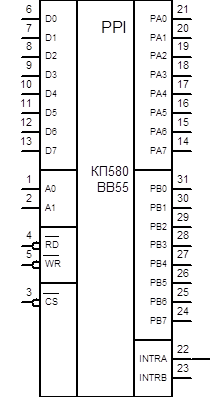

Описание контроллера параллельных ПУ КР580ВВ55.

Используется для организации параллельного обмена данными между процессором и ПУ. Позволяет подключать до 2 устройств.

Назначение выводов: D7 – D0 – двунаправленная шина данных; А0,А1 – адресные входы для выбора требуемого ПУ; RD,WR – выбор операций чтения или записи; CS – выбор данной микросхемы; PA7 – PA0, PB7 - PB0 – шины данных к ПУ; INTA, INTB – выводы запросов на прерывания.

|

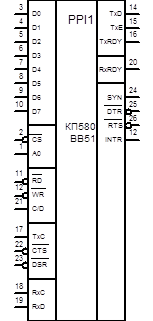

Описание контроллера последовательных ПУ КР580ВВ51.

|

Предназначен для реализации синхронно-асинхронных приемо-передач между последовательными ПУ и процессором.

4. Разработка принципиальной схемы

Принципиальная схема МПВК приведена в приложении схема 3.

В схеме используется микропроцессор фирмы Intel 80386. Он имеет двадцатичетырехразрядную шину адреса, но так как восемь старших разрядов не используются, то они заведены на землю. В данной реализации мы обходимся шестнадцатью разрядами адреса, так как адресуемая память имеет размер 640 кбайт. Сигналы, необходимые для работы с сопроцессором также не используются.

Для реализации буферного шестнадцатиразрядного регистра используются два восьмиразрядных регистра КП580ИР82.

Для реализации шестнадцатиразрядного шинного формирователя используются два восьмиразрядных формирователя КП580ВА86.

ПЗУ на 256 кбайта собрано на микросхемах КР556РТ4 емкостью 32 кбайта.

ОЗУ на 640 кбайт собрано на микросхемах КР185РУ5 емкостью 256 кбайт.

Заключение

Проблема повышение быстродействия ЭВМ наиболее ощутима в настоящее время, так как повышение быстродействия за щет изобретения новых микросхем или использования новых технологий в настоящее время почти невозможно. Приходится решать эту проблему используя уже существующую базу. Многопроцессорный комплекс является одним из наиболее успешных решений данной проблемы.

В данном курсовом проекте не использовались отдельные каналы ввода-вывода для подсоединения ПУ непосредственно к памяти, а использовалось подключение через системную шину. Это дало бы возможность полностью освободить системную шину и предоставить ее полностью в распоряжение компьютера. Единственный недостаток оставшийся в МПВК после этого – это простои процессоров в случае одновременного обращения к памяти. Эта проблема решается за счет действительно многопортового ОЗУ.

Литература

1. Ларионов А. М. и др. Вычислительные комплексы, системы и сети. - Л. : Энергоатомиздат, 1987.

2. Цифровые интегральные микросхемы: Справ. / Богданович М. И. и др. – Мн. : Беларусь, 1991.

3. Конопелько В. К. , Лосев В. В. надежное хранение информации в полупроводниковых ЗУ. – М. Радио и связь, 1986.

4. Полупроводниковые БИС запоминающих устройств: Справочник / под ред. А. Ю. Горбунова – М. : Радио и связь, 1986.

5. Левкин В.Г.,Левкина А.И. Введение в схемотехнику IBM PC/AT. – Мн. : Беларусь,1982.

6. Руководство по архитектуре IBM PC/AT,/ под ред. М.Л. Мархасина. – Мн. : 1993.

7. Качан М.К. Электронные вычислительные машины и системы. Киев.1985.

8. Русак И.М.,Луговской К.Л. Технические средства ПЭВМ. Справочник. Москва. 1984.

9. Микропроцессорный комплекс К1810: структура, программирование, применение. Справочник. Москва. Высшая школа. 1990.