Организация прерываний в ЭВМ

СОДЕРЖАНИЕ: Проектирование механизма обработки прерываний. Контроллер прерываний Intel 82C59A. Ввод-вывод по прерыванию. Программируемый контроллер интерфейса Intel 82C55A. Роль процессора в обработке прерывания ввода-вывода. Обзор алгоритма обработки прерывания.ФЕДЕРАЛЬНОЕ АГЕНСТВО ПО ОБРАЗОВАНИЮ

Брянский государственный технический университет

Курсовая работа

по Организации ЭВМ

На тему: «Организация прерываний в ЭВМ».

Выполнил:

№

Проверил:

Новозыбков 2007г.

Содержание

Введение

Ввод-вывод по прерыванию

Обработка прерывания

Проектирование механизма обработки прерываний

Контроллер прерываний Intel 82C59A

Программируемый контроллер интерфейса Intel 82C55A

Заключение

Приложение

Список литературы

Введение

Одной из разновидностей программно-управляемого обмена данными с ВУ в микроЭВМ является обмен с прерыванием программы, отличающийся от асинхронного программно-управляемого обмена тем, что переход к выполнению команд, физически реализующих обмен данными, осуществляется с помощью специальных аппаратных средств. Команды обмена данными в этом случае выделяют в отдельный программный модуль - подпрограмму обработки прерывания. Задачей аппаратных средств обработки прерывания в процессоре микроЭВМ как раз и является приостановка выполнения одной программы (ее еще называют основной программой) и передача управления подпрограмме обработки прерывания. Действия, выполняемые при этом процессором, как правило, те же, что и при обращении к подпрограмме. Только при обращении к подпрограмме они инициируются командой, а при обработке прерывания - управляющим сигналом от ВУ, который называют Запрос на прерывание или Требование прерывания.

Эта важная особенность обмена с прерыванием программы позволяет организовать обмен данными с ВУ в произвольные моменты времени, не зависящие от программы, выполняемой в микроЭВМ. Таким образом, появляется возможность обмена данными с ВУ в реальном масштабе времени, определяемом внешней по отношению к микроЭВМ средой. Обмен с прерыванием программы существенным образом экономит время процессора, затрачиваемое на обмен. Это происходит за счет того, что исчезает необходимость в организации программных циклов ожидания готовности ВУ, на выполнение которых тратится значительное время, особенно при обмене с медленными ВУ. Прерывание программы по требованию ВУ не должно оказывать на прерванную программу никакого влияния кроме увеличения времени ее выполнения за счет приостановки на время выполнения подпрограммы обработки прерывания. Поскольку для выполнения подпрограммы обработки прерывания используются различные регистры процессора (счетчик команд, регистр состояния и т.д.), то информацию, содержащуюся в них в момент прерывания, необходимо сохранить для последующего возврата в прерванную программу.

Обычно задача сохранения содержимого счетчика команд и регистра состояния процессора возлагается на аппаратные средства обработки прерывания. Сохранение содержимого других регистров процессора, используемых в подпрограмме обработки прерывания, производится непосредственно в подпрограмме. Отсюда следует достаточно очевидный факт: чем больший объем информации о прерванной программе сохраняется программным путем, тем больше время реакции микроЭВМ на сигнал прерывания, и наоборот. Предпочтительными с точки зрения повышения производительности микроЭВМ (сокращения времени выполнения подпрограмм обработки, а, следовательно, и основной программы) являются уменьшение числа команд, обеспечивающих сохранение информации о прерванной программе, и реализация этих функций аппаратными средствами. Формирование сигналов прерываний - запросов ВУ на обслуживание происходит в контроллерах соответствующих ВУ. В простейших случаях в качестве сигнала прерывания может использоваться сигнал Готовность ВУ, поступающий из контроллера ВУ в системный интерфейс микроЭВМ. Однако такое простое решение обладает существенным недостатком - процессор не имеет возможности управлять прерываниями, т. е. разрешать или запрещать их для отдельных ВУ. В результате организация обмена данными в режиме прерывания с несколькими ВУ существенно усложняется.

Целью данной работы является определение организации прерывания в ЭВМ, а задачами: а) изучение обработки прерывания, б) изучение проектирования механизма прерывания, в) определение контроллера прерывания.

Ввод-вывод по прерыванию

Мы уже отмечали, что методика программируемого ввода-вывода приводит не рациональному расходованию времени процессора, который фактически простаивает, выжидая, пока внешнее устройство завершит начатую операцию. В результате страдает производительность вычислительной системы.

Альтернативная методика предполагает, что процессор, дав команду модулю. Ввода-вывода на выполнение операции, сам переключается на выполнение какой-либо другой задачи или фрагмента программы. В свою очередь, модуль ввода-вывода, получив от процессора команду, выполняет необходимые операции и, завершив их, формирует сигнал запроса прерывания, который передается процессору и извещает его о том, что выполнение затребованной операции окончено. После этого процессор возвращается к выполнению ранее прерванной программы и, если это предусмотрено в программе, пересылает полученные данные в память.

Рассмотрим, как реализуется эта методика. Начнем с операций, выполняемых модулем ввода-вывода. При вводе данных модуль получает от процессора команду READ. Затем модуль самостоятельно выполняет все действия, необходимые для того, Чтобы получить от внешнего устройства очередную порцию данных и записать ее в свой буфер После этого модуль формирует сигнал запроса прерывания процессора на одной из линий управления системной магистрали и ждет, пока от процессора не поступит команда выставить содержимое регистра на линии данных. Когда такой сигнал поступает, модуль выставляет информацию на линии данных и после этого готов принять следующую команду обмена от процессора.

Участие процессора во всей этой процедуре выглядит следующим образом. Во-первых процедура начинается по инициативе процессора, который передает модулю команду READ. После этого процессор может перейти к выполнению дальнейших инструкций программы, не связанных с затребованными данными (ответственность зато, что в этих инструкциях не используются данные, которые ожидается получить от внешнего устройства, возлагается на программиста), или вообще переключиться на выполнение другой программы. В конце каждого цикла выполнения инструкции. Процессор проверяет, не поступил ли сигнал запроса прерывания. Если окажется, что такой сигнал поступил от модуля ввода-вывода, процессор выполняет операции, сохраняющие текущий контекст выполняемой программы (т.е. состояние счетчика команд и внутренних регистров), и переключается на программу прерывания. Эта программа, в частности, может выполнять считывание данных с модуля ввода-вывода и передачу их в оперативную память. После завершения программы обработки прерывания процессор восстанавливает сохраненный контекст прерванной программы и возобновляет ее выполнение с той же точки, как будто никакого прерывания и не было.

Алгоритм ввода данных по прерыванию исключает простои процессора в ожидании завершения операции медленно работающим внешним устройством, а потому способствует эффективному использованию ресурсов процессора в интересах повышения производительности всей системы. Но, тем не менее, и эта процедура имеет резерв для повышения производительности, поскольку она предусматривает, что все данные, вводимые в систему или выводимые из нее на внешнее устройство, обязательно проходят через процессор.

Обработка прерывания

Рассмотрим более детально роль процессора в обработке прерывания ввода вывода. Появление сигнала запроса прерывания запускает несколько процессов, часть которых реализуется аппаратными средствами, а часть — программными. В Приложении рис.1 представлен типичный алгоритм обработки прерывания. После завершения модулем ввода-вывода заданной операции на аппаратном уровне выполняются следующие действия:

1. Модуль ввода-вывода формирует сигнал запроса прерывания, который предназначается процессору.

2. Процессор завершает выполнение текущей команды программы, прежде чем анализировать наличие сигнала запроса прерывания.

3. Процессор анализирует, не поступил ли сигнал запроса прерывания, обнаруживает его и посылает сигнал подтверждения тому модулю, который сформировал сигнал запроса. Получив сигнал подтверждения, модуль, инициировавший прерывание, снимает соответствующий сигнал с линии управления магистрали,

4. Процессор выполняет действия, предшествующие передаче управления по программе обработки прерывания. Прежде всего нужно позаботиться о сохранении текущего состояния процессора, что позволит в дальнейшем возобновить выполнение прерванной программы с той же точки. Здесь нужно обратить внимание на то, что в этот момент в счетчике команд процессора находится адрес команды, которая должна была бы выполняться процессором, если бы не произошло прерывание. Эту команду (а точнее, ее адрес) принято называть точкой прерывания, и она же является точкой возврата из прерывания. Поэтому процессор должен каким-то образом сохранить состояние счетчика команд, регистра состояния, который содержит слово состояния процессора PSW( processor status word ). Как правило, эта информация помещается в системный стек.

5. Затем процессор загружает в счетчик команд начальный адрес программы (подпрограммы) обработки прерывания. В разных компьютерах и разных операционных системах эта операция выполняется по-разному. В одних — каждый источник прерывания (модуль ввода-вывода, вызвавший прерывание) имеет свою подпрограмму обработки, в других — прерывания разбиты на группы и каждая группа имеет свою программу обработки, а в третьих — вообще существует одна программа обработки всех прерываний, внутри которой происходит ветвление в соответствии с конкретным источником прерывания. Если архитектура системы предусматривает наличие множества подпрограмм обработки прерываний, то информацию о том, какую именно подпрограмму нужно вызывать в каждом конкретном случае, процессор должен получать вместе с самим сигналом запроса прерывания. Другой вариант процессор получает ее от устройства, инициировавшего прерывание, в ответ на сигнал подтверждения. Как только в счетчик команд будет помещен адрес подпрограммы, процессор начнет новый цикл выполнения команды. Первой фазой цикла будет извлечение команды, адрес которой находится в счетчике. В результате процессор приступит к выполнению заданной подпрограммы обработки прерывания. Что именно будет при этом сделано, определяет программист, который разработал подпрограмму.

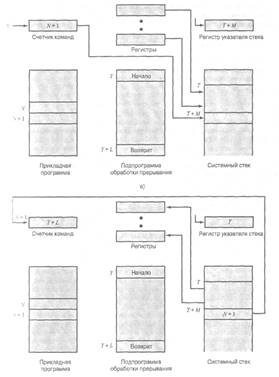

6. Перед передачей управления подпрограмме обработки прерывания процессор аппаратными средствами выполнил сохранение счетчика команд и PSW в системном стеке. Но помимо этой информации для возобновления прерванной программы может потребоваться и восстановление состояния других регистров процессора. Поэтому, как правило, первые команды подпрограммы обработки сохраняют в стеке состояния всех остальных регистров процессора, поскольку они могут понадобиться самой подпрограмме и, следовательно, их содержимое к моменту завершения подпрограммы будет изменено. В Приложении рис.2 (а) показано, что при этом происходит. В данном случае пользовательская программа была прервана в тот момент, когда выполняла команду, хранящуюся по адресу N. Аппаратно в стек помещается содержимое счетчика команд, каким оно было в момент завершения выполнения этой команды — N+1, а в счетчик команд заносится начальный адрес подпрограммы обработки Y. Сама подпрограмма затем помещает в стек содержимое регистров процессора, в результате чего указатель стека смещается и после завершения сохранения регистров будет указывать на ячейку Т.

7. После этого подпрограмма приступает к собственно обработке прерывания Этот процесс, как правило, включает анализ состояния модуля ввода-вывода, вызвавшего прерывание, и прием или передачу порции данных Иногда в процессе обработки модулю посылаются другие команды или сообщения, в частности команды запуска следующего сеанса обмена, если передается большой блок данных.

8. После завершения обработки подпрограмма восстанавливает содержимое в регистрах, которое было сохранено в стеке в самом начале выполнения подпрограммы (Приложение рис.2 (б)), и только после этого выполняет последнюю команду — команду возврата из прерывания.

9. Выполнение команды возврата из прерывания сводится к восстановление из стека слова состояния программы PSW и счетчика команд. В результате состояние регистров процессора полностью восстанавливается в том виде, каким оно было в момент обнаружения прерывания.

Обращаю ваше внимание на то, что очень важно перед началом обработки прерывания сохранить всю информацию, необходимую для продолжения выполнения прерванной программы. Прерывание может возникнуть в любой момент, и подпрограмме обработки прерывания абсолютно неизвестно, какую именно программу она прервала, какие регистры процессора эта программа использовала, а какие нет. Надежное функционирование вычислительной системы, имеющей дело с прерываниями, может быть гарантировано только, если аппаратными и программными средствами предусмотрено полное сохранение состояния системы в момент прерывания и последуют — его восстановление.

Проектирование механизма обработки прерываний

При проектировании механизма обработки прерываний в конкретной вычислительной системе нужно решить два важных вопроса: как передать процессору информацию об источнике прерывания и как должен поступить процессор в случае, если одновременно возникают прерывания от нескольких источников.

Сначала рассмотрим проблему идентификации источника прерывания, в практике проектирования компьютерных систем применяется четыре варианта решения:

• включение в состав системной магистрали нескольких линий передачи сигналов прерывания;

• программный опрос;

• последовательное включение источников в цепь распространения сигнала предоставления прерывания (аппаратный опрос);

• арбитраж магистрали.

Естественно, самый простой подход — предоставить каждому потенциальному источнику отдельную линию передачи сигнала запроса прерывания. Но практически удается выделить для этой цели всего несколько линий, хотя потому что количество контактов микросхемы процессора ограничено. Следовательно, в чистом виде этот подход можно реализовать только в специализированных компьютерах с заранее заданным составом модулей ввода-вывода. Иногда поступают по-другому — разделяют потенциальные источники прерывай на ограниченное число групп, каждой из которых предоставляется своя линия распространения сигналов запроса прерываний. Но внутри группы в таком случае должен быть использован один из трех оставшихся подходов.

Один из таких подходов предполагает программный опрос источников - модулей ввода-вывода — при получении процессором сигнала запроса прерывания. Опрос выполняется в самом начале выполнения подпрограммы обработки прерывания, сразу же за сохранением состояния регистров процессор стеке. Для того чтобы такой опрос был возможен, в составе системной магистрали должна быть предусмотрена отдельная линия для передачи сигнала опроса (линия TESTI/0), а в наборе команд процессора — соответствующая команда, аргументом которой является адрес модуля ввода-вывода. При выполнении этой команды процессор формирует сигнал опроса на линии TESTI/O, сопровождая его кодом адреса модуля ввода-вывода на линиях адреса. Если опрашиваемый модуль действительно был источником прерывания, он выставляет сигнал подтверждения, который фиксируется в одном из битов слова состояния PSW. Следующая команда условного перехода анализирует этот бит и выполняет переход на ветвь обработки данного прерывания. Опрашивая по очереди все потенциальные источники прерывания, программа может таким образом найти, какой из них был инициатором данного прерывания. Другой вариант реализации этой идеи состоит в том, что в регистре состояния каждого модуля ввода-вывода предусматривается специальный бит, который устанавливается аппаратно, если данный модуль формирует сигнал прерывания. Опрашивая по очереди регистры состояния модулей, программа может выяснить, какой же из них послал сигнал запроса прерывания, и перейти на соответствующую ветвь. Недостаток метода программного опроса тот же, что и программно управляемого ввода-вывода, — процессор теряет время на опрос всех потенциальных источников прерываний.

Альтернативой программному опросу является аппаратный опрос, который реализуется последовательным включением источников в цепь распространения сигнала предоставления прерывания. При такой организации образуется цепочка источников — daisy chain , - в которой каждое звено (модуль ввода-вывода) пропускает дальше сформированный процессором сигнал предоставления прерывания, если сам он источником прерывания не является. Если же модуль ранее сформировал сигнал запроса прерывания, то, получив сигнал предоставления, он дальше его не пропускает, а выставляет собственный вектор прерывания — специфичный именно для данного устройства код — на линии данных магистрали. В результате процессор, опросив линии данных через некоторое время после формирования сигнала предоставления прерывания, получит информацию о том, кто же именно « осмелился его побеспокоить». Как правило, вектор прерывания содержит адрес подпрограммы обработки данного прерывания, но иногда это может быть просто уникальный идентификатор модуля. В любом случае полученный вектор прерывания несет процессору или программе информацию, достаточную для того, чтобы однозначно распознать источник прерывания, и соответственно на него реагировать. Прерывания, сопровождаемые передачей в том или ином виде уникального кода, идентифицирующего источник прерывания, принято называть векторными ( vectored interrupt ).

Существует и другой вариант реализации идеи векторного прерывания — с помощью арбитра магистрали. В этом случае прежде чем сформировать сигнал запроса прерывания, модуль ввода-вывода стремится захватить управление магистралью — стать задатчиком. Механизм арбитража магистрали, предоставляющий право стать задатчиком одному из конкурентов, если их окажется несколько. В его основе лежит та же идея последовательного соединения претендентов в цепочку. Получив от арбитра магистрали право быть задатчиком, модуль выставляет сигнал запроса прерывания и в ответ на сигнал предоставления прерывания от процессора выставляет код собственного вектора прерывания на линии данных.

Описанные выше методы не только позволяют выяснить, какой же из модулей ввода-вывода является возмутителем спокойствия, но и ранжировать их по приоритету в случае, если несколько модулей одновременно попытаются вызвать прерывание. Если в вычислительной системе используется несколько линий запроса прерывания, то каждая из них может иметь свой приоритет, и в аппаратуре процессора предусматривается, что предпочтение будет отдано источнику прерывания, подключенному к линии с более высоким приоритетом. При программном опросе приоритет источников закладывается в последовательность опроса потенциальных источников — те из них, которые имеют более высокий приоритет, опрашиваются раньше менее привилегированных. Программный подход фактически перекладывает ответственность за назначение приоритетов на плечи системного программиста. Если используется метод аппаратного опроса источников, то приоритет зависит от места каждого из них в цепочке распространения сигнала предоставления прерывания — чем ближе модуль к процессору (который в данном случае является боссом), тем выше его приоритет (в компьютерном мире многое устроено так же, как у людей). Об обсуждения концепций организации ввода-вывода перейдем к рассмотрению двух конкретных примеров.

Контроллер прерываний Intel 82 C 59 A

Микропроцессор Intel 80386 поддерживает работу с одной линией запроса прерывания (INTR) и одной линией сигнала предоставления прерывания (INTA). Для того чтобы процессор Intel 80386 мог обслуживать множество внешних устройств, к нему подключается внешний контроллер прерываний Intel 82C59A, к которому, в свою очередь, подключаются модули управления внешними устройствами. Контролер Intel 82С59А в данном случае играет роль арбитра прерываний.

В Приложении рис.3представлена схема подключения множества модулей ввода-вывода к процессору Intel 803S6 через контроллер прерываний Intel 82С59А Отдельный контроллер Intel 82C59A может обслуживать до восьми модулей ввода-вывода. Если в компьютере предполагается использовать более восьми модулей, контроллеры включаются по каскадной схеме и в результате могут обслуживать до 64 модулей.

Единственная задача контроллера Intel 82C59A — обслуживание прерываний. Он получает сигналы запроса прерываний от подключенных модулей ввода-вывода, анализирует, какое из устройств, одновременно приславших запрос. имеет наивысший приоритет, и передает сигнал запроса прерывания на линию INTR, подключенную непосредственно к процессору. Процессор отвечает сигналом предоставления прерывания на линии INTA. В ответ контроллер помещает вектор соответствующего прерывания на линии данных. После этого процессор начинает выполнять процедуру обработки прерывания и работает напрямую с модулями ввода-вывода — считывает или передает данные.

Режим работы контроллера Intel 82C59A, а именно схема назначения приоритетов, программируется процессором. Существуют три варианта режима назначения приоритетов.

• Вложенный ( fully nested ). Приоритет запроса определяется тем, к какому контакту контроллера подключен сигнал. Тот из них, который подключен ко входу IRO, имеет приоритет 0, а подключенный ко входу IR7 — приоритет 7.

• Циклический ( rotating ). В некоторых приложениях нескольким внешним устройствам (группе) назначается один и тот же приоритет. В этом режиме после получения сигнала предоставления прерывания модуль, инициировавший прерывание, получает самый низкий приоритет в группе.

• Маскируемый ( special mask ). В этом режиме процессор может заблокировать прерывания от выбранных устройств, передав специальный код маски.

Программируемый контроллер интерфейса Intel 82 C 55 A

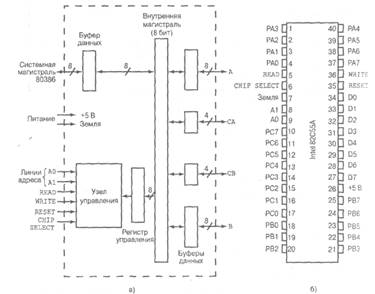

Программируемый контроллер интерфейса Intel 82C55A может служить прекрасным примером модуля, используемого как в режиме программируемого ввода-вывода, так и в режиме ввода-вывода по прерыванию. Модуль выполнен в виде БИС в корпусе с 40 выводами и предназначен для работы с микропроцессором Intel 80386. В Приложении рис.4 представлена блок-схема контроллера и назначение выводов.

Внешнее устройство подключается к контроллеру через 24 линии связи, показанные на схеме справа. Сигналы на этих линиях определяются состоянием внутренних регистров контроллера, которые программируются процессором Intel 80386. Процессор может задавать через регистры управления разные режимы работы контроллера. 24 выходных линии разбиты на три группы по 8 линий в каждой — группы А, В и С. Каждая группа может функционировать как отдельный 8-разрядный порт ввода-вывода. Кроме того, группа С разбита на две подгруппы — СА и СВ, — которые можно использовать в сочетании с портами А и В соответственно. Если контроллер будет сконфигурирован таким способом, то подгруппы са и СВ смогут передавать (принимать) сигналы управления и состояния, а порты — сигналы данных на ввод и на вывод.

Слева на схеме представлены линии интерфейса, по которым контроллер обменивается сигналами с процессором через системную магистраль. В их числе входят 8 двунаправленных линий передачи данных (линии DO-D7), по которым передаются (принимаются) данные в порты ввода-вывода и в регистры управления. Обмен данными выполняется, когда установлен сигнал CHIPSELECT и один из сигналов READ или WRITE. Сигнал RESET устанавливает контроллер в исходное состояние.

Загружая тот или иной код в регистр управления, процессор способен задавать режим работы контроллера и конфигурацию порта С. В режиме 0 три группы выходных линий контроллера работают как три независимых 8-разрядных порта, каждый из которых может быть сконфигурирован либо как порт ввода, либо как порт вывода. Другой вариант конфигурации — группы линий А и В работают как порты ввода-вывода, а группа линий С делится на две, одна из которых становится группой передачи сигналов управления, поддерживающих порт А, а другая — порт В. Сигналы управления предназначены для выполнения двух основных процедур — обмена сигналами при установлении связи (процедура «handshaking» — рукопожатие) и формирования сигнала запроса прерывания. В первом случае реализуется самый простой алгоритм синхронизации. Одна управляющая линия используется для передачи сигнала готовности DATAREADY,который означает, что данные выставлены на внешние линии данных. Другая линия используется для приема сигнала подтверждения ACKNOWLEDGE, который является индикатором того, что выставленные ранее данные считаны и соответствующие сигналы можно сбросить. Еще одна линия предназначена для передачи сигнала запроса прерывания INTERRUPTREQUEST и подключается непосредственно к соответствующей линии системной магистрали.

Поскольку режим работы контроллера Intel 82C55A программируется извне, его можно настроить на работу с самыми разными несложными внешними устройствами. В Приложении рис.5 показано, как с помощью этого контроллера можно реализовать управление клавиатурой и дисплеем видеотерминала. Клавиатура рассматривается как устройство ввода, передающее 8-разрядный код. Два разряда, shiftи CONTROL, имеют особое значение для программы обслуживания клавиатуры, которая выполняется процессором. Однако особая интерпретация этих ; разрядов никак не затрагивает контроллер — это не его заботы. Он передает эти разряды дальше на линии данных системной магистрали точно так же, как и шесть остальных. Для синхронизации обмена с клавиатурой выделены две сигнальных линии — DATAREADY И ACKNOWLEDGE.

Дисплей также подключен к контроллеру через 8-разрядный порт данных. Набор управляющих линий включает, помимо DATAREADY и ACKNOWLEDGE, еще две дополнительных.

Заключение

Приоритет ВУ в микроЭВМ с программным опросом готовности внешнего устройства однозначно определяется порядком их опроса в подпрограмме обработки прерываний. Чем раньше в подпрограмме опрашивается готовность ВУ, тем меньше время реакции на его запрос и выше приоритет. Необходимость проверки готовности всех внешних устройств существенно увеличивает время обслуживания тех ВУ, которые опрашиваются последними. Это является основным недостатком рассматриваемого способа организации прерываний. Поэтому обслуживание прерываний с опросом готовности ВУ используется только в тех случаях, когда отсутствуют жесткие требования на время обработки сигналов прерывания внешних устройств. Организация системы прерываний в микроЭВМ с использованием векторов прерываний позволяет устранить указанный недостаток. При такой организации системы прерываний ВУ, запросившее обслуживания, само идентифицирует себя с помощью вектора прерывания - адреса ячейки основной памяти микроЭВМ, в которой хранится либо первая команда подпрограммы обслуживания прерывания данного ВУ, либо адрес начала такой подпрограммы. Таким образом, процессор, получив вектор прерывания, сразу переключается на выполнение требуемой подпрограммы обработки прерывания. В микроЭВМ с векторной системой прерывания каждое ВУ должно иметь собственную подпрограмму обработки прерывания.

Различают векторные системы с интерфейсным и внеинтерфейсным вектором. В первом случае вектор прерывания формирует контроллер ВУ, запросившего обслуживания, во втором - контроллер прерываний, общий для всех устройств, работающих в режиме прерываний (IBM-совместимые персональные компьютеры).

Аппаратный опрос готовности ВУ производится гораздо быстрее, нежели программный. Но если обслуживания запросили одновременно два или более ВУ, обслуживание менее приоритетных ВУ будет отложено на время обслуживания более приоритетных, как и в системе прерывания с программным опросом. Рассмотренная векторная система прерываний практически полностью соответствует системе прерываний, реализованной в микроЭВМ Электроника-60. Восьмиразрядный вектор прерывания в Электронике-60 указывает одну из ячеек памяти с адресами от 0 до (376)8, в которой размещается адрес начала подпрограммы обработки прерывания.

В следующей за указанной вектором прерывания ячейке памяти хранится новое содержимое регистра состояния процессора, загружаемое в него при переключении на подпрограмму обработки прерывания. Один из бит нового содержимого регистра состояния процессора запрещает или разрешает прерывания от других ВУ, что позволяет ВУ с более высоким приоритетом прерывать подпрограммы обслуживания ВУ с меньшим приоритетом и наоборот. Векторная система с внеинтерфейсным вектором прерывания используется в IBM-совместимых персональных компьютерах. В этих компьютерах контроллеры внешних устройств не имеют регистров для хранения векторов прерывания, а для идентификации устройств, запросивших обслуживания, используется общий для всех ВУ контроллер прерываний

Приложение

Алгоритм обработки прерывания.

Изменение состояния памяти и регистров процессора в процессе обработки прерывания: а — вход в подпрограмму обработки прерывания; б — завершение подпрограммы обработки прерывания.

Схема подключения контроллеров прерываний INTEL 82C59A к микропроцессору INTEL 80386

Программируемый контроллер интерфейса INTEL82C55A: а)блок-схема; б) назначение выводов микросхем.

Подключение клавиатуры и дисплея контроллеру интерфейса INTEL 82C55A.

Список литературы

1. Духнич Е.И., Андреев А.Е., Организация вычислительных машин и систем:Учебн. пособие/ВолгГТУ, Волгоград, 2003.-80с.

2. Луценко Е.В. «Вычислительные машины» - Краснодар. 2000.

3. Тертышный В.Т. «История персонального компьютера» - М. 2002.

4. Уильям Столлингс «Структурная организация и архитектура компьютерных систем». - М 2002г.

5. www.intuit.ru – “Интернет Университет”, портал дистанционного образования.