Резисторы

СОДЕРЖАНИЕ: Схемотехнические параметры. Конструктивно–технологические данные. Классификация интегральных микросхем и их сравнение. Краткая характеристика полупроводниковых интегральных микросхем. Расчёт полупроводниковых резисторов, общие сведения об изготовлении.Содержание

Введение …………………………………………………………………………. 4

1. Исходные данные для проектирования …………………………………....... 6

1.1. Схемотехнические параметры …….…………………………………....... 6

1.2. Конструктивно – технологические данные для проектирования .………. 6

2. Обзор литературы по теме курсового проекта ………………………….... 12

2.1. Классификация интегральных микросхем и их сравнение ………….... 12

2.2. Краткая характеристика полупроводниковых интегральных микросхем16

3. Расчёт полупроводниковых резисторов ………………………………….... 18

3.1. Общие сведения об изготовлении полупроводниковых резисторов …. 18

3.2. Порядок расчёта полупроводниковых резисторов …………………….. 22

3.3. Расчёт полупроводниковых резисторов ………………………………... 26

4. Проектирование топологии ИМС ………………………………………….. 28

5. Выводы о проделанной работе ……………………………………………... 35

Список используемой литературы…………………………………………….. 36

Введение

Поскольку ИС, подобно электронной лампе или транзистору, представляет собой конструктивно единое целое, выполняет определенную функцию и должна удовлетворять определенным требованиям при испытаниях, поставках и эксплуатации, она относится к разряду электронных приборов. Однако по сравнению с диодом, транзистором и т, п. ИС является качественно новым типом прибора.

Первая – главная особенность ИС как электронного прибора состоит в том, что она самостоятельно выполняет законченную, часто весьма сложную функцию, тогда как элементарные электронные приборы выполняют аналогичную функцию только в ансамбле с другими компонентами. Например, отдельный транзистор не может обеспечить усиление сигнала или запоминание информации. Для этого нужно из нескольких транзисторов, резисторов и других компонентов собрать (спаять) соответствующую схему, В микроэлектронике же указанные функции выполняются одним прибором — интегральной схемой: она может быть усилителем, запоминающим устройством и т. п.

Второй важной особенностью ИС является то, что повышение функциональной сложности этого прибора по сравнению с элементарными не сопровождается ухудшением какого-либо из основных показателей (надежность, стоимость и т. п.). Более того, все эти показатели улучшаются. Проиллюстрируем эту особенность на примере полупроводниковых ИС.

Поскольку габариты и масса простых и средних ИС близки к габаритам и массе дискретных транзисторов, можно считать, что в первом приближении выигрыш по этим показателям при переходе от дискретных схем к интегральным определяется степенью интеграции и может достигать сотен и тысяч раз.

Поскольку надежность работы полупроводникового прибора в аппаратуре определяется, прежде всего, количеством паяных и (в меньшей степени) (парных соединении, то ИС, у которых межсоединения элементов осуществляются путем металлизации (т. е. без папки и сварки), обладают заведомо повышенной надежностью по сравнению с дискретными схемами, выполняющими ту же функцию. По мере увеличения степени интеграции этот выигрыш возрастает,

Стоимость ИС при прочих равных условиях близка к стоимости одного транзистора. Значит, в зависимости от степени интеграции (или, точнее, от плотности упаковки), стоимость одного элемента ИС по сравнению со стоимостью аналогичного дискретного компонента может быть в сотни раз меньше.

Третья особенность ИС состоит в предпочтительности активных элементов перед пассивными – принцип, диаметрально противоположный тому, который свойствен дискретной транзисторной технике. В последней активные компоненты, особенно транзисторы, наиболее дорогие, и потому оптимизация схемы при прочих равных условиях состоит в уменьшении количества активных компонентов. В ИС дело обстоит иначе: у них задана стоимость не элемента, а кристалла; поэтому целесообразно размещать на кристалле как можно больше элементов с минимальной площадью. Минимальную площадь имеют активные элементы – транзисторы и диоды, а максимальную – пассивные. Следовательно, оптимальная ИС – это ИС, у которой сведены к минимуму количество и номиналы резисторов и, особенно, конденсаторов.

Четвертая особенность ИС связана с тем, что смежные элементы расположены друг от друга на расстоянии всего 50 – 100 мкм. На таких малых расстояниях различие электрофизических свойств материала маловероятно, а следовательно, маловероятен и значительный разброс параметров у смежных элементов. Иначе говоря, параметры смежных элементов взаимосвязаны – коррелированны.. Эта корреляция сохраняется к при изменении температуры: у смежных элементов температурные коэффициенты параметров практически одинаковы. Корреляция между параметрами смежных элементов используется при проектировании некоторых ИС с целью снизить влияние разброса параметров и изменений температуры.

1. Исходные данные для проектирования.

Схемотехнические параметры.

|

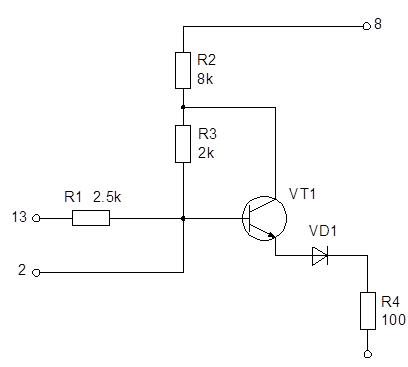

На рисунке 1 изображена электрическая схема варианта № 29.

Рис.1 Электрическая схема варианта 29.

1.2 Конструктивно – технологические данные и ограничения.

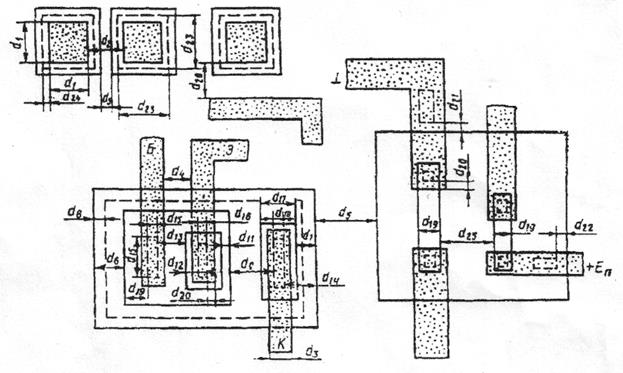

Конструктивные и технологические ограничения, которые учитываются при разработке топологии интегральной микросхемы на биполярных транзисторах, изображены на рисунке 2. Расшифровка рисунка приведена в таблице 1.

Рис. 2 Конструктивно-технологические ограничения при разработке топологии интегральной микросхемы на биполярных транзисторах.

Таблица 1

Конструктивно-технологические данные и ограничения.

| Минимально допустимые размеры | Мкм |

| Ширина линии скрайбирования слоя | 60 |

Расстояние от центра скрайбирующей полосы до края слоя металлизации или до края диффузионной области |

50 - 100 |

| Ширина проводника d3 при длине 50 мкм | 4 |

| Расстояние между проводниками d4 при длине 50 мкм | 3 |

| Перекрытие металлизации контактных окон в окисле к элементам ИМС d20 | 2 |

| Расстояние от края контактного окна р+ разделительных областей для подачи смещения до края области разделения d21 | 6 |

| Расстояние от края контактного окна к изолированным областям n-типа для подачи смещения до края области разделения d22 | 6 |

| Размер контактных площадок для термокомпрессионной приварки проводников d 1 | 100 |

| Расстояние между контактными площадками d2 | 70 |

Продолжение таблицы 1

| Расстояние между проводниками d 4 при длине 50 мкм | 4 |

| Размер контактных площадок текстовых элементов рабочей схемы | 50x50 |

| Размеры контактного окна к базе d 15 | 4x6 |

| Размеры контактного окна к эмиттеру d 16 | 4х4;3х5 |

| Размеры окна вскрытия в окисле | 2,5x2,5 |

| Размеры окна в пассивирующем окисле d 23 | 100x100 |

| Ширина области разделительной диффузии d 5 | 4 |

| Расстояние от базы до области подлегирования разделительной диффузии d 6 | 10 |

| Расстояние между краем области подлегирования коллекторного контакта и краем разделительной области d7 | 10 |

| Расстояние между краем разделительной области и краем скрытого n+ – слоя d 8 | 7 |

| Расстояние между краем контактного окна в окисле и к базе и 3 краем базы d 1 | 3 |

| Расстояние между эмиттерной и базовой областями d 11 | 3 |

Расстояние между краем контактного окна в окисле к эмиттеру и краям эмиттера dl |

3 |

| Расстояние между контактными окнами к базе и эмиттеру | 4 |

| Расстояние между базовыми областями, сформированными в одном коллекторе | 9 |

| Расстояние между контактным окном к коллектору и областью разделительной диффузии d 14 | 6 |

| Ширина области подлегирования n+ – слоя в коллекторе d 17 | 8 |

| Ширина к контактному окну к коллектору dl8 | 4 |

| Ширина резистора d 13 | 5 |

| Ширина диффузионной перемычки | 3 |

| Расстояние от края окна в пассивации до края контактной площадки d 20 | 6 |

| Расстояние между соседними резисторами d 25 | 7 |

| Расстояние между диффузионными и ионно-легированными резисторами | 4 |

| Расстояние между контактной площадкой и проводящей дорожкой d 26 | 20 |

| Ширина скрытого n+ – слоя | 4 |

| Расстояние между контактными площадками текстовых элементов | 40 |

| Перекрытие металлизации контактных окон в окисле к элементам ИМС d2o | 2 |

| Расстояние от края контактного окна р+ к разделительным областям для подачи смещения до края области разделения d 2 1 | 6 |

| Расстояние от края контактного окна к изолированным областям n-типа для подачи смещения до края области разделения d 22 | 6 |

Следует обращать особое внимание на размеры топологических зазоров, так как при неоправданно малых их значениях ИМС или не будет функционировать, из-за перекрытия областей структуры (например, базовой области и области разделительной диффузии), или будет иметь искаженные параметры за счет усиления паразитных связей между элементами. С другой стороны, завышение размеров топологических зазоров топологических зазоров приводит к увеличению кристалла.

Сущность работы по созданию топологии ИМС сводится к нахождению такого оптимального варианта расположения элементов схемы, при котором обеспечиваются высокие показатели эффективности производства и качества ИМС: низкий уровень бракованных изделий, низкая стоимость, материалоемкость, высокая надежность, соответствие получаемых электрических параметров заданным.

Количество и размеры изолированных областей оказывают существенное влияние на характеристики ИМС, поэтому:

1. Суммарная площадь изолирующих p-n-переходов должна

быть минимальной, так как их емкость является паразитной. Минимальные размеры изолированной области определяются геометрическими размерами находящихся в ней элементов и зазорами, которые необходимо выдерживать между краем изолированной области и элементами и между самими элементами, размещенными в одной изолированной области;

2. К изолирующим р-n-переходам всегда должно быть приложено напряжение обратного смещения, что практически осуществляется подсоединением подложки р-типа, или области разделительной диффузии р-типа, к точке схемы с наиболее отрицательным потенциалом. При этом суммарное обратное напряжение, приложенное к изолирующему переходу не должно превышать напряжения пробоя;

3. Диффузионные резисторы, формируемые на основе базового слоя, можно располагать в одной изолированной области, которая подключается к точке схемы с наибольшим положительным потенциалом. Обычно такой точкой является контактная площадка ИМС, на которую подается напряжение смещения от коллекторного источника питания;

4. Резисторы на основе эмиттерного и коллекторного слоев следует располагать в отдельных изолированных областях;

5. Транзисторы типа n-p-n, коллекторы которых подсоединены непосредственно к источнику питания, целесообразно размещать в одной изолированной области вместе с резисторами;

6. Транзисторы типа n-p-n, которые включены по схеме с общим коллектором, можно располагать в одной изолированной области;

7. Все другие транзисторы, кроме упомянутых в п. 5 и 6 необходимо располагать в отдельных изолированных областях, т.е. все

коллекторные области, имеющие различные потенциалы, должны быть изолированы;

8. Для уменьшения паразитной ёмкости между контактными площадками и подложкой, а также для защиты от короткого замыкания в случае нарушения целостности пленки окисла под ними при приварке проволочных выводов под каждой контактной площадкой создают изолированную область, за исключением контактных площадок с наиболее отрицательных потенциалом;

9. Количество изолированных областей для диодов может сильно изменяться в зависимости от типа диодов и способов их включения. Если в качестве диодов используются переходы база-коллектор, то для каждого диода требуется изолированная область, так как каждый катод (коллекторная область n-типа) должен иметь отдельный вывод;

10. Для диффузионных конденсаторов требуются отдельные изолированные области. Исключение составляют случаи, когда один из выводов конденсатора является общим с другой изолированной областью;

11. Для диффузионных перемычек всегда требуются отдельные и изолированные области.

2. Обзор литературы по теме курсового проекта.

2.1. Классификация интегральных микросхем и их сравнение.

В процессе развития микроэлектроники (МЭ), начиная с 1960 г., номенклатура ИС непрерывно изменялась. При этом отдельные типы ИС нередко рассматривались как альтернативные, т. е. исключающие все другие. В настоящее время каждый из основных типов ИС занял свое, относительное стабильное место в микроэлектронике. Выше, иллюстрируя общую идею интеграции, мы имели в виду главный тип ИС – полупроводниковые.

Классификация ИС. По способу изготовления и получаемой при этом структуре различают два принципиально разных типа интегральных схем: полупроводниковые и плёночных.

Классификация ИС. По способу изготовления и получаемой при этом структуре различают два принципиально разных типа интегральных схем: полупроводниковые и плёночных.

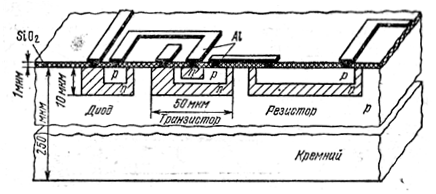

Рис.3. Структура элементов полупроводниковой ИС.

Полупроводниковая ИС – это микросхема, элементы которой выполнены в приповерхностном слое полупроводниковой подложки (рис.3). Эти ИС составляют основу современной микроэлектроники.

Полупроводниковая ИС – это микросхема, элементы которой выполнены в приповерхностном слое полупроводниковой подложки (рис.3). Эти ИС составляют основу современной микроэлектроники.

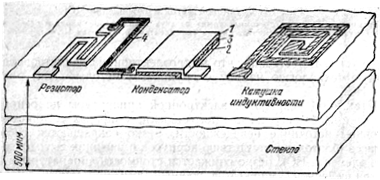

Рис.4. Структура элементов пленочной ИС: 1– верхняя обкладка; 2– нижняя обкладка; 3– диэлектрик; 4– соединительная металлическая полоска.

Пленочная ИС — это микросхема, элементы которой выполнены в виде разного рода пленок, нанесенных на поверхность диэлектрической подложки (рис.4). В зависимости от способа нанесения пленок и связанной с этим их толщиной различают тонкопленочные ИC (толщина пленок до 1 – 2 мкм) и толстопленочные ИС (толщина пленок от 10 – 20 мкм и выше).

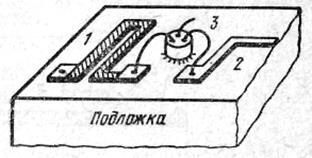

Поскольку до сих пор никакая комбинация напыленных пленок не позволяет получить активные элементы типа транзисторов, пленочные ИС содержат только пассивные элементы (резисторы, конденсаторы и т. п.). Поэтому функции, выполняемые чисто пленочными ИС, крайне ограничены. Чтобы преодолеть эти ограничения, пленочную ИС дополняют активными дискретными компонентами, располагая их на той же подложке и соединяя с пленочными элементами (рис.5). Тогда получается смешанная – пленочно-дискретная ИС, которую называют гибридной.

Гибридная ИС (или ГИС) – это микросхема, которая представляет собой комбинацию пленочных пассивных элементов и дискретных активных компонентов, расположенных на общей диэлектрической подложке. Дискретные компоненты, входящие в состав гибридной ИС, называют навесными, подчеркивая этим их обособленность от основного технологического цикла получения пленочной части схемы. Помимо диодов и транзисторов, навесными компонентами могут быть и полупроводниковые ИС, т. е. компоненты повышенной функциональной сложности.

Еще один тип «смешанных» ИС, в которых сочетаются полупроводниковые и пленочные интегральные элементы, называют совмещенными.

Еще один тип «смешанных» ИС, в которых сочетаются полупроводниковые и пленочные интегральные элементы, называют совмещенными.

Рис.5. Структура гибридной ИС: 1– резистор; 2– полоска металлизации; 3– навесной бескорпусный транзистор.

Совмещенная ИС – это микросхема, у которой активные элементы выполнены в приповерхностном слое полупроводникового, кристалла (как у полупроводниковой ИС), а пассивные нанесены в виде пленок на предварительно изолированную поверхность того же кристалла (как у пленочной ИС).

Совмещенные ИС выгодны тогда, когда необходимы высокие номиналы и высокая стабильность сопротивлений и емкостей; эти требования легче обеспечить с помощью пленочных элементов, чем с помощью полупроводниковых.

Во всех типах ИС межсоединения элементов осуществляются с помощью тонких металлических полосок, напыленных или нанесенных на поверхность подложки и в нужных местах, контактирующих с соединяемыми элементами. Процесс нанесения этих соединительных полосок называют металлизацией, а сам «рисунок» межсоединений – металлической разводкой.

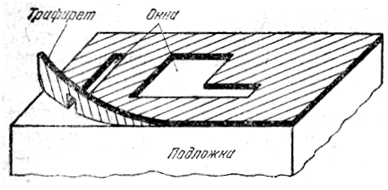

Толстопленочные ГИС (обозначим их ТсГИС) изготавливаются весьма просто, на первый взгляд – примитивно. На диэлектрическую пластинку-подложку довольно большой площади (несколько квадратных сантиметров) наносят пасты разного состава. Характерная особенность этого метода состоит в том, что пленка сразу приобретает заданную толщину. Проводящие пасты обеспечивают межсоединения элементов, обкладки конденсаторов и выводы к штырькам корпуса; резистивные – получение резисторов; диэлектрические – изоляцию между обкладками конденсаторов и общую защиту поверхности готовой ГИС. Каждый слой должен иметь свою конфигурацию, свой рисунок. Поэтому при изготовлении каждого слоя пасту наносят через свою маску – трафарет – с отверстиями (окнами) в тех местах, куда должна попасть паста данного слоя (рис, 6). После того как пленочная часть ТсГИС закончена, на заранее отведенные «пустые» места или на защитный диэлектрический слой приклеивают навесные компоненты и соединяют их выводы с контактными площадками, предусмотренными в проводящих слоях.

Из приведенного краткого описания следуют главные особенности ТсГИС:

— «механический» способ нанесения паст не позволяет делать толщину пленок менее 10 – 20 мкм (типичные значения 50 – 100 мкм), отсюда – названия толстопленочная технология и толстопленочные ГИС;

— простота технологии обеспечивает ее доступность и низкую стоимость изделий;

— «механический» способ нанесения пленок не может обеспечить достаточно малых допусков на номиналы резисторов и конденсаторов, т. е. прецизионность элементов.

Рис.6. Накладная маска – трафарет для локального нанесения пасты.

Тонкопленочные ГИС (обозначим их ТкГИС) изготавливаются по более сложной технологии, чем ТсГИС, причем используется специфическое оборудование, обычно весьма дорогое. Поэтому стоимость ТкГИС выше, чем ТсГИС.

Классическая тонкопленочная технология характерна тем, что пленки осаждаются на подложку из газовой фазы. При этом пленки приобретают свою конечную толщину не сразу (как после нанесения пасты в ТсГИС), а постепенно – один мономолекулярный слой за другим. Вырастив очередную пленку, меняют химический состав газа и тем самым электрофизические свойства следующей пленки. Таким образом, поочередно получают проводящие, резистивные и диэлектрические слои. Конфигурация (рисунок) каждого слоя определяется либо трафаретом, наложенным на подложку (как в случае ТсГИС), либо маской, выращенной на поверхности подобно окисной маске в полупроводниковых ИС.

Для того чтобы атомы или молекулы пара беспрепятственно проходили от источника до подложки, необходимо создать достаточное разрежение атмосферы, т.е. проводить осаждение (нанесение) пленок в замкнутом пространстве (под колпаком), в котором создан вакуум той или иной степени.

Навесные элементы в ТкГИС, как и в ТсГИС, приклеивают на поверхность готовой пленочной части схемы и соединяют с соответствующими контактными площадками элементов.

2.2. Краткая характеристика полупроводниковых микросхем.

В настоящее время различаю два класса полупроводниковых ИС: биполярные ИС и МДП ИС. Сочетание биполярных и МДП – транзисторов на одном кристалле является особым случаем.

Технология полупроводниковых ИС обоих классов основана на легировании полупроводниковой (кремниевой) пластины поочередно донорными и акцепторными примесями, в результате чего под поверхностью образуются тонкие слои с разным типом проводимости и р–n – переходы на границах слоев. Отдельные слои используются в качестве резисторов, а р–n – переходы – в диодных и транзисторных структурах.

Легирование пластины приходится осуществлять локально, т.е. на отдельныхучастках, разделенных достаточно большими расстояниями. Локальное легирование осуществляется с помощью специальных масок с отверстиями, через которые атомы примеси проникают в пластину на нужных участках. При изготовлении полупроводниковых ИС роль маски обычно играет пленка двуокиси кремния SiO2 , покрывающая поверхность кремниевой пластины. В этой пленке специальными методами гравируется необходимая совокупность отверстий или, как говорят, необходимый рисунок. Отверстия в масках, в частности в окисной пленке, называют окнами.

Полупроводниковые микросхемы характеризуются рядом недостатков. В частности, в полупроводниковом материале трудно получать пассивные элементы с заданными номинальными значениями. Кроме того, они имеют низкую температурную стабильность, что усложняет конструирование схем, и сильные паразитные связи между элементами, вызывающие ухудшение качества схем.

Несмотря на отмеченные недостатки, полупроводниковые микросхемы в настоящее время относятся к числу наиболее перспективных изделий микроэлектроники, так как они позволяют создавать надежные малогабаритные и сложные в функциональном отношении схемы. При использовании хорошо отработанных технологических методов изготовления полупроводниковые микросхемы оказываются значительно надежнее и дешевле схем из навесных элементов. Полупроводниковые микросхемы выпускаются промышленностью на основе биполярных и МДП структур.

3. Расчет полупроводниковых резисторов.

3.1. Общие сведения об изготовлении полупроводниковых резисторов.

В полупроводниковых микросхемах функцию резистора выполняет объем полупроводника, имеющий определенные размеры и конфигурацию, или транзисторная схема (аналог резистора). Интегральные резисторы могут быть разделены на следующие типы в зависимости от структуры: диффузионные (на основе эмиттерной или базовой области); эпитаксиальные (на основе коллекторной области); пинч – резисторы, а также резисторы, изготовляемые методом ионного легирования. Все интегральные резисторы, кроме последнего из перечисленных типов, изготовляются одновременно с активными элементами микросхем без введения дополнительных этапов обработки. Они создаются на основе коллекторной, базовой или эмиттерной областей транзистора.

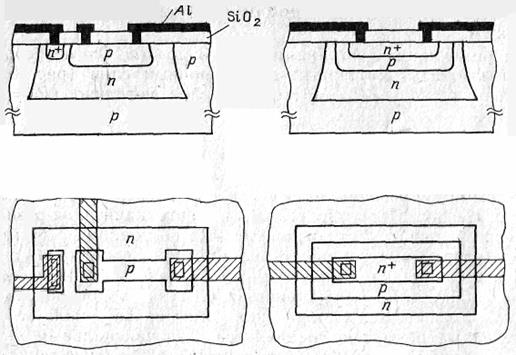

Диффузионные резисторы. Диффузионные резисторы изготавливают одновременно с диффузией примесей, в процессе которой создаются базовые или эмиттерные области n-р-n – транзистора. Сопротивление диффузионного резистора представляет собой объемное сопротивление участка диффузионного слоя, ограниченного p-n – переходом. Оно определяется геометрическими размерами резистивной области и распределением примеси по глубине диффузионного слоя, которое, в свою очередь, характеризуется удельным поверхностным сопротивлением RS . Значение RS является конструктивным параметром резистора; зависящим от технологических факторов (режима диффузии). Типичные значения сопротивления диффузионных резисторов, которые можно получить при данном значении RS , лежит в пределах 4Rs R 104 RS . Нижний предел ограничивается сопротивлением контактных областей, которое должно быть значительно меньше сопротивления основной области резистора. В качестве контактирующего металла используется алюминий. Верхний предел ограничивается допустимой площадью, отводимой под резистор. Чаще всего резисторы выполняются на основе базовой области (RS = 100 – 300 Ом/). В этом случае в качестве резистора используется область р – типа (рис. 7). К слою n – типа прикладывается положительный потенциал, смещающий р–n – переход в обратном направлении. Обратносмещенный переход, обладающий большим сопротивлением, определяет границы диффузионной области и обеспечивает развязку по постоянному току между резистором и подложкой. На основе базового диффузионного слоя можно получать резисторы с номиналами сопротивлений от 100 Ом до 60 кОм.

Для резисторов с номиналами от 3 до 100 Ом целесообразно использовать эмиттерный диффузионный слой поскольку значение RS эмиттерного слоя невелико (RS = l– 10 Ом/).

а) б)

Рис.7. Структуры диффузионных резисторов: а – резистор на основе базовой области; б – резистор на основе эмиттерной области.

Пинч-резисторы. При необходимости создания высокоомных резисторов с сопротивлением более 60 кОм используют пинч-резисторы (канальные, сжатые или закрытые). Пинч – резисторы могут создаваться на основе базового слоя или коллекторного. Резистор представляет собой тонкий канал р –типа, используется донная, слаболегированная часть базовой области с RS = 2 – 5 кОм/, изолированная со всех сторон обратносмещенным р–n– переходом, так как эмиттерный слой n+ – типа за пределами резистора соединяется с эпитаксиальным n – слоем изолированной области. Максимальное сопротивление таких резисторов составляет 200 – 300 кОм при простейшей полосковой конструкции. Для получения качественного омического контакта используют диффузионные n – области, которые создают на стадии эмиттерной диффузии. Пинч – резисторы имеют большой разброс номиналов (до 50%) из-за трудностей получения точных значений толщины донной части, сопротивление их сильно зависит от температуры вследствие малой степени легирования областей, на основе которых они выполняются.

Эпитаксиальные резисторы. Из трех областей транзистора коллекторная имеет наименьшую концентрацию легирующей примеси и максимальное RS (500—5000 Ом/). Поскольку эпитаксиальный слой легирован однородно, проводимость эпитаксиального резистора постоянна по всему сечению в отличие от диффузионных резисторов. У эпитаксиального резистора поперечное сечение по форме существенно отличается от сечений диффузионных резисторов, так как эпитаксиальный резистор формируется разделительной диффузией. Поскольку эта диффузия самая продолжительная и точная регулировка размеров диффузионных областей, особенно величины боковой диффузии, затруднена, разброс номиналов сопротивления эпитаксиальных резисторов значителен. Эти резисторы имеют большой ТКС, поскольку коллекторная область легирована слабо. Таким образом, если в микросхеме можно использовать некритичные резисторы с высокими номинальными значениями, то их целесообразно формировать на основе эпитаксиального слоя, что позволит сэкономить площадь кристалла.

Ионно-легированные резисторы. Высокоомные резисторы, занимающие малую площадь на кристалле, можно получить, используя метод ионной имплантации. Поверхностное сопротивление резисторов, изготовленных методом ионного легирования, при соответствующем выборе дозы легирования и режиме термообработки может составлять от 500 Ом/ до 20 кОм/. Абсолютное значение удельного поверхностного сопротивления может выдерживаться с точностью ±6%. Температурные коэффициенты сопротивления резисторов, полученных методом ионного легирования, обычно меньше ТКС диффузионных резисторов. Структура ионно-легированных резисторов такая же, как и диффузионных резисторов, но глубина ионно-легированных слоев составляет 0,1– 0,3 мкм. Создание диффузионных р- или n- областей необходимо для получения качественных омических контактов. Низкий ТКС, высокое удельное сопротивление и хорошая совместимость с другими элементами позволяют использовать ионно-легированные резисторы для изготовления прецизионных аттенюаторов, а также в микромощных микросхемах. Типичные характеристики интегральных резисторов приведены в табл. 2.

Таблица 2

Характеристики интегральных резисторов.

| Тип резистора | RS Ом/ | Разброс,R, % | ТКС (R ), 1/о С |

| Диффузионный резистор на основе эмиттерной области | 1 – 10 | ± 20 | ± (1 – 5) · 10-4 |

| Диффузионный резистор на основе базовой области | 100 – 300 | ± (5 – 20) | ± (1,5 – 3) · 10-3 |

| Пинч-резистор на основе базового слоя | (2 – 5) · 108 | ± 50 | ± (1,5 – 3) · 10-3 |

| Пинч-резистор на основе коллекторного слоя | (4 – 8) · 103 | ± 50 | ± (3 – 4) · 10-3 |

| Эпитаксиальный резистор | (0,5 – 5) · 103 | ± (15 – 25) | ± (2 – 4) · 10-3 |

| Ионно-легированный резистор n-типа | (5 – 10) · 102 | 10 | ± (0,5 – 1,5) · 10-3 |

| Ионно-легированный резистор р-типа | (0,5 – 20) · 103 | 10 | ± (1 – 2) · 10-3 |

3.2. Порядок расчета полупроводниковых резисторов.

Как уже отмечалось, один из способов реализации резистивных элементов в полупроводниковых микросхемах заключается в использовании диффузионных слоев, полученных при формировании базовых или эмиттерных областей транзисторов. Кроме того, применяются эпитаксиальные и ионно-легированные резисторы.

Исходными данными для определения геометрических размеров интегральных полупроводниковых резисторов являются:

а) заданные в принципиальной электрической схеме номинальное значение Rи допуск на него yR = R/R;

б) поверхностное сопротивление легированного слоя Rs , на основе которого формируется резистор;

в) средняя мощность, рассеиваемая резистором Р, и максимально допустимая удельная мощность Ро.

г) основные технологические и конструктивные ограничения. Сопротивление резистора R — Rs l/b, где l и b — длина и ширина резистора.

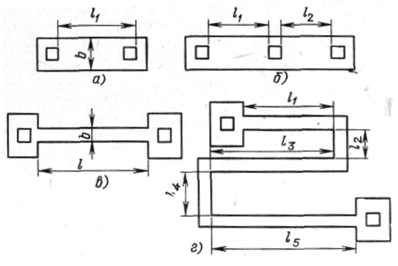

Проектирование резистора с заданным номиналом сводится к определению конфигурации резистивного слоя, так как при известном поверхностном сопротивлении слоя Rs номинальное значение сопротивления резистора зависит от отношения его длины к ширине (коэффициента формы Кф = l/b). Контактные площадки, расположенные на концах полупроводникового резистора, вносят дополнительные сопротивления. Поэтому в расчетную формулу вводится поправочный коэффициент, зависящий от конфигурации контактных областей. На рис. 8. приведены несколько типовых топологий полупроводниковых резисторов. Конфигурации, приведенные на рис. 8, а, б, пригодны для реализации низкоомных резисторов с номинальными значениями от нескольких ом до одного килоома. При этом оказывается, что для очень низкоомных резисторов ширина превышает его длину.

R = Rs (l/b + 2k1 ),(1)

R = Rs((li + k)/b-b3k1 )

где k1 = 0,07 — поправочный коэффициент.

Для резисторов с номинальными значениями, превышающими 400 Ом, можно использовать топологию, приведенную на рис. 8, в. Расчетное соотношение для определения сопротивления резистора в этом случае

R = Rs(l/b + 2k2 ),(2)

где k2 = 0,65 – поправочный коэффициент.

Резисторам с номинальными значениями более 1 кОм целесообразно придавать форму змейки (рис. 8, г), что позволяет значительно уменьшить площадь, занимаемую резистором. Изгибы резистора оказывают влияние на его значение, что учитывается используемым для этого случая расчетным соотношением

R = Rs(l /b + 2·0,65 + n0,55),(3)

где l – суммарная длина прямоугольных участков; п – число изгибов резистора на угол 90 °.

Рис.8. Топологии диффузионных резисторов: а, б – низкоомные до 1 кОм; в, г – свыше 400 Ом.

Расчет геометрических размеров интегральных полупроводниковых резисторов начинают с определения их ширины. За ширину резистора принимают значений, которое не меньше наибольшего значения одной из следующих величин:

минимальной ширины резистора bтех , определяемой разрешающей способностью технологических процессов (bтех = 3,5 – 4 мкм);

минимальной ширины резистора bточн , при которой точность его изготовления равна заданной;

минимальной ширины резистора bР определяемой исходя из максимально допустимой рассеиваемой мощности:

bрас макс (bтех , bточн , bР ).(4)

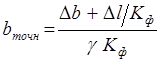

Ширина резистора

где b, l– абсолютные погрешности ширины и длины резистивной полоски (для типовых технологических процессов b = l = 0,05 – 0,1 мкм); Кф –коэффициент формы, определяется из соотношения Kф = R/Rs; кФ – относительная погрешность коэффициента формы резистора:

кФ = R –RS – T (5)

Здесь RS =Rs/Rs– относительная погрешность удельного поверхностного сопротивления легированного слоя (для типовых технологических процессов RS = 0,05 – 0,1); T = R (Тмакс = = 20°С) – температурная погрешность сопротивления.

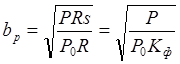

Минимальное значение ширины bР определяется как’

(6)

(6)

где Pо – максимально допустимая удельная мощность рассеяния, выбираемая в зависимости от типа корпуса микросхемы и условий ее эксплуатации в пределах 0,5 – 4,5 Вт/мм.

Расчетную длину резистора определяют исходя из формулы (1).

Для составления топологического чертежа определяют вначале промежуточные значения ширины и длины резистора, учитывающие технологические отклонения размеров:

bпром = bрасч – 2трав – xj (7)

bпром = lрасч – 2трав – xj (8)

где трав – погрешность, вносимая за счет систематического растравления контактных окон в окисле (для типовых технологических процессов трав = 0,1 – 0,5 мкм); x – погрешность, вносимая за счет ухода базовой (эмиттерной) диффузии под окисел в боковую сторону. Через обозначен коэффициент, учитывающий распределение примесей вблизи границы резистора, причем обычно 0 2. Для резисторов шириной более 10 мкм боковой диффузией можно пренебречь ( = 0). В более узких резисторах боковая диффузия оказывает значительное влияние, поэтому в расчеты необходимо вводить соответствующую поправку.

Затем выбирают шаг координатной сетки d(d = 0,l; 0,2; 0,5; 1 мм) и, задаваясь масштабом 100:1, 200:1 и т. д., определяют топологические значения ширины и длины резистора:

bтоп = Kb d bпром (9)

lтоп = Kl d bпром (10)

где Кb , Kl – целые положительные числа.

После этого оценивают получающуюся погрешность

R = [R(lтоп , bтоп ) – R] / R,(11)

где R(lтоп , bтоп ) – сопротивление, рассчитанное по (1) при l– lтоп ; b= bтоп .

Если R R зад , то ширину резистора увеличивают на величину dи все вычисления повторяют.

3.3. Расчет полупроводниковых резисторов.

Все расчеты проводятся по упрощенной схеме с использованием табличных значений из справочника. Выбираем ширину базовой области для резистора:

1) Низкоомные резисторы с номиналом R 1 кОм имеет ширину базовой области = 30 мкм;

2) Высокоомные резисторы с номиналом от 1 кОм до 5 кОм (1 кОм R 5 кОм) выполняются с шириной базового слоя = 20 мкм;

3) Высокоомные резисторы с номиналом R 5 кОм выполняются с шириной базовой области = 15 мкм.

Таким образом, достигается воспроизводимость параметров резисторов в объеме партии вследствие малого влияния боковой диффузии и погрешностей технологических операций.

Из справочных данных принимаем следующие величины удельного поверхностного сопротивления s :

1) при 100 Ом R 300 Ом s =120 Ом/

2) при 300 Ом R 2,5 кОм s =222 Ом/

3) при 3 кОм R 4 кОм s =320 Ом/

4) при 5 кОм R 10 кОм s =240 Ом/

Составим таблицу значений (таблица 3)

Таблица 3

| Позиция | R 1 | R 2 | R 3 | R 4 |

| Номинал, Ом | 2500 | 8000 | 2000 | 100 |

Ширина диффузионной области , мкм |

20 | 15 | 20 | 30 |

| Удельное поверхностное сопротивление, s , Ом/ | 222 | 240 | 222 | 120 |

Исходя из того, что коэффициент формы «n» можно представить двумя формулами:

и

и  (12)

(12)

приравниваем правые части этих уравнений:

где – ширина резистора, l – длинна резистора

где – ширина резистора, l – длинна резистора

Формула для расчета длины резистора l:

(13)

(13)

Все величины, входящие в формулу, нам известны, поэтому рассчитаем длину каждого из резисторов.

1) ![]()

Так как для чертежа топологии взят масштаб 400:1, то переведем величины 1 и l1 в мм:

l1 = 400 · 225.2 мкм = 90 080 мкм = 90 мм

1 = 400 · 20 мкм = 8 000 мкм = 8 мм

2) ![]()

l2 = 400 · 500 мкм = 200 000 мкм = 200 мм

2 = 400 · 15 мкм = 6 000 мкм = 6 мм

3) ![]()

l3 = 400 · 180.2 мкм = 72 080 мкм = 72 мм

3 = 400 · 20 мкм = 8 000 мкм = 8 мм

4) ![]()

l4 = 400 · 25 мкм = 10 000 мкм = 10 мм

4 = 400 · 30 мкм = 12 000 мкм = 12 мм

4. Проектирование технологии ИМС.

Основные правила проектирования топологии полупроводниковых микросхем с изоляцией р-n-переходом

Важнейший этап проектирования полупроводниковой микросхемы заключается в преобразовании ее электрической схемы в топологию. Сущность разработки топологии микросхем состоит в определении взаимного расположения элементов на подложке. Разработка топологии не сводится к размещению элементов на подложке. Этот процесс должен осуществляться так, чтобы обеспечить оптимальное расположение элементов, при котором уменьшается влияние паразитных эффектов, присущих полупроводниковым микросхемам. Поэтому одной из основных задач при разработке топологии микросхемы является выбор критерия оптимальности размещения элементов. В настоящее время при разработке топологии полупроводниковых микросхем с однослойной металлизацией обязательными считаются следующие критерии: минимизация общей суммарной длины соединений; минимизация числа пересечений межэлементных соединений.

Как уже отмечалось, разработка топологии микросхем производится в несколько этапов. После расчета геометрических размеров активных и пассивных элементов приступают к разработке эскиза топологии микросхем, который вычерчивается от руки в произвольном масштабе, но с сохранением приближенного соотношения габаритных размеров элементов. При разработке эскиза топологии в первую очередь определяют число изолированных областей (карманов), которые при изоляции обратносмещенным р-n-переходом создают с помощью разделительной диффузии акцепторных примесей. Таким образом, изолированная область представляет собой область n-типа, которая соответствует коллектору транзистора. Анализируя принципиальную электрическую схему, определяют число коллекторов, имеющих различные потенциалы. Этим числом в основном и обусловлено число необходимых изолированных областей.

При разработке эскиза топологии микросхем площади изолированных областей делают как можно меньшими. Это позволяет, во-первых, реализовать на пластине большое количество микросхем и, во-вторых, уменьшить паразитные емкости переходов коллектор – подложка, влияющих на их параметры. Минимальная площадь изолированной области зависит от геометрических размеров размещаемых в ней элементов, а также расстояний, которые необходимо выдерживать между краем изолированной области и элементом и между элементами. В свою очередь, геометрические размеры областей самих элементов микросхем (эмиттера, коллектора, базы и т. д.) определяются требованиями, предъявляемыми к их электрическим характеристикам и параметрам, а также технологическими возможностями.

Минимальное расстояние между областями элементов (топологические зазоры) определяют с учетом следующих факторов, возникающих в рабочем режиме микросхем: расширения обедненной области р-n-переходов; паразитного взаимодействия между областями. Кроме того, необходимо учитывать, что реальные размеры структурных элементов, а следовательно, и топологические зазоры между областями элементов зависят от ухода p-n-перехода под окисел, т. е. от эффекта боковой диффузии. Очевидно, что для определения топологических зазоров нужно учесть погрешности, присущие определенному технологическому процессу изготовления микросхем.

Технологические погрешности в основном возникают при проведении фотолитографических процессов, а также при диффузии. Ошибка, обусловленная процессом фотолитографии, состоит из неточностей, возникающих при изготовлении фотошаблонов, из размерной ошибки проявленного изображения, связанной с режимом экспонирования, и размерной ошибки, возникающей при травлении SiO2 , а также из-за неточности совмещения фотошаблона с подложкой. Топологические зазоры должны быть оптимизированы, так как при неоправданно малых топологических зазорах может произойти перекрытие отдельных областей, например области разделительной диффузии и базовой области, вследствие чего схема не будет функционировать. В этом случае возрастает также паразитное взаимодействие между областями элементов. В частности, может возникнуть паразитный транзистор со структурой база – коллектор – область разделительной диффузии. Чем меньше зазор база – подложка, тем больше коэффициент усиления по току у этого паразитного латерального транзистора. С другой стороны, завышение топологических зазоров приводит к увеличению площади, занимаемой микросхемой. Например, при завышении топологических зазоров всего лишь на 0,5 мкм площадь транзистора возрастает приблизительно на 12 мкм2 , а если микросхема содержит 50 транзисторов, то площадь, занимаемая микросхемой, увеличивается на 600 мкм2 , что представляет весьма существенный вклад в потери площади.

Необходимо отметить, что обычный подход при расчете топологических зазоров, т.е. с точки зрения наихудшего случая, применяется довольно редко, чаще всего используется метод, основанный на сборе статистического распределения погрешностей. Топологические ограничения непрерывно изменяются по мере совершенствования технологических процессов изготовления микросхем.

Конструирование и выбор структуры интегральных транзисторов. Процесс проектирования планарных транзисторов состоит из следующих этапов: для данной серии ИМС или нескольких серий, исходя из быстродействия, потребляемой мощности, необходимой степени интеграции, задают электрические параметры транзисторов как базовых элементов ИМС; выбирают технологию производства ИМС, параметры материала подложки и эпитаксиального слоя, приближенно оценивают основные размеры конструкции транзисторов в плане и в сечении, проводят расчет электрических параметров транзисторов и, если они существенно отличаются от заданных, путем ступенчатого изменения конструктивных размеров и последующих расчетов подбирают геометрию всех областей транзисторной структуры, не выходя за рамки технологических ограничений. Затем осуществляют экспериментальную проверку проведенной работы: разрабатывают комплект фотошаблонов, выпускают опытные партии транзисторных структур и измеряют их характеристики. Если параметры транзисторов отличаются от заданных, то методом последовательных приближений путем изменения размеров транзисторных областей и их характеристик, корректировки режимов технологических процессов добиваются необходимого соответствия параметров.

Расчет транзисторов сложен, трудоемок, без применения ЭВМ практически невыполним, точность его невысока. Поэтому часто этап расчета конструкции транзисторов опускают, акцентируя внимание на экспериментальном этапе. При этом на предприятии, выпускающем ИМС, формируют банк интегральных транзисторов с широким спектром характеристик. При таком подходе задача конструктора ИМС состоит в подборе конкретных типов интегральных транзисторов для данной ИМС в соответствии с ее электрической схемой.

1. Сначала выбирают физическую структуру различных областей транзистора. Удельное сопротивление подложки должно быть большим (1—10 Ом · см), что обеспечивает высокое напряжение пробоя и малую емкость обратно смещенного p-n-перехода коллекторной подложки.

2. При выборе уровня легирования коллекторной области (эпитаксиального слоя) необходимо выполнить ряд противоречивых требований: для получения малого последовательного сопротивления коллектора уровень его легирования должен быть высокий, а для получения малой емкости и высокого напряжения пробоя перехода база – коллектор – низкий.

Обычно удельное сопротивление эпитаксиального слоя выбирают равным 0,1 – 0,5 Ом см, а толщину – в пределах 2 – 15 мкм. Использование тонких эпитаксиальных слоев (до 3 мкм) позволяет уменьшить паразитные емкости и увеличить плотность размещения элементов. В структурах со скрытым n+ – слоем и подлегированием области коллекторного контакта последовательное сопротивление коллектора составляет 10—50 Ом.

3. При выборе уровней легирования базовой и эмиттерной областей необходимо также учитывать несколько противоречивых требований. Так, для уменьшения паразитного сопротивления между активной областью базы и контактом к базе следует увеличивать уровень легирования базы. Однако это приводит к снижению эффективности эмиттера и уменьшению напряжения пробоя перехода база – эмиттер. Кроме того, поверхностная концентрация примеси в базовом слое не должна быть меньше 5·1016 см -3 , так как на поверхности этого слоя возможно образование инверсного проводящего канала n-типа, индуцированного встроенным зарядом в окисле.

4. Высокий уровень легирования эмиттера необходим для получения большого коэффициента инжекции. Однако при уровнях легирования эмиттерной области, достигающих предела растворимости примеси в кремнии, в кристаллической решетке образуются точечные и линейные дефекты, которые значительно уменьшают время жизни носителей заряда, что, в свою очередь, приводит к уменьшению коэффициента инжекции.

5. Частотные характеристики транзисторов зависят в основном от паразитных емкостей переходов и последовательных сопротивлений его областей. Влияние паразитных параметров уменьшают конструктивно за счет максимально возможного уменьшения геометрических размеров транзистора.

6. После выбора физической структуры выбирают конфигурацию транзистора. Поскольку характеристики в значительной степени зависят от размеров различных областей транзистора, нужно учитывать, что периметр эмиттера определяет токовые характеристики транзистора, площадь эмиттера – частотные характеристики, площадь базы – емкость перехода база – коллектор и распределенное сопротивление базы, площадь коллектора – емкость перехода коллектор – подложка и последовательное сопротивление коллектора.

7. Обычно анализируют несколько типовых конфигураций транзисторов, где сплошными линиями обозначены границы диффузионных областей, а пунктирными – границы вскрытия окон в пленке двуокиси кремния для последующего формирования металлических контактов. Для микромощных схем наиболее пригодна полосковая конструкция транзистора

Взаимное расположение контактов к различным областям транзисторной структуры выбирают в зависимости от конкретного топологического рисунка микросхемы и удобства расположения выводов транзистора. Если необходимо получить малое сопротивление коллектора, применяют транзисторы с увеличенной контактной областью к коллектору. Для получения малого сопротивления базы и высокого коэффициента усиления используют конструкции с двумя контактами к базовой области. Многоэмиттерные транзисторы применяют во входных цепях схем транзисторно-транзисторной логики (ТТЛ).

На основе эскиза разрабатывают предварительный вариант топологии, который вычерчивают на миллиметровой бумаге в выбранном масштабе, обычно 100:1 или 200:1 (выбирают масштабы, кратные 100). Топологию проектируют в прямоугольной системе координат. Каждый элемент топологии представляет собой замкнутую фигуру со сторонами, состоящими из отрезков прямых линий, параллельных осям координат. Придание элементам форм в виде отрезков прямых линий, не параллельных осям координат, допустимо только в тех случаях, когда это приводит к значительному упрощению формы элемента. Например, если форма элемента состоит из ломаных прямых, составленных в виде «ступенек» с мелким шагом, рекомендуется заменить их одной прямой линией. Координаты всех точек, расположенных в вершинах углов ломаных линий, должны быть кратны шагу координатной сетки.

При вычерчивании чертежа топологии на миллиметровой бумаге принимают минимальный шаг координатной сетки, равный 0,5 мм. Можно выбрать другой шаг, но он должен быть кратным минимальному. Действительный (на кристалле) размер шага координатной сетки зависит от выбранного масштаба топологии.

При вычерчивании общего вида топологии рекомендуется использовать линии разного цвета для различных слоев ИМС: эмиттерного – черный, базового – красный, разделительного (коллекторного) – зеленый, вертикального – черный пунктирный, скрытого – зеленый пунктирный, металлизации – желтый, окна в окисле для контакта к элементам – синий пунктирный, окна в пассивирующем (защитном) окисле – синий сплошной.

В процессе вычерчивания топологии для получения оптимальной компоновки возможно изменение геометрии пассивных элементов, например пропорциональное увеличение длины и ширины резисторов или их многократный изгиб, позволяющие провести над резистором полоски металлической разводки или получить более плотную упаковку элементов. При изменении формы пассивных элементов в процессе их размещения проводят корректировочные расчеты в соответствии с формулами и рекомендациями.

Проверка правильности разработки топологии ИМС. Последний из составленных и удовлетворяющий всем требованиям вариант топологии подвергают проверке в такой последовательности. Проверяют соответствие технологическим ограничениям: минимальных расстояний между элементами, принадлежащими одному и разным слоям ИМС.

5. Выводы о проделанной работе.

В данном курсовом проекте разработана топология интегральной микросхемы.

Разработанная мной топология соответствует электрической принципиальной схеме, учитывая топологические ограничения, и использует исходные конструктивные данные.

Для изготовления заданной схемы была выбрана планарная технология на кремниевой пластине. Изоляция элементов схемы осуществляется с помощью обратно смещённого р-n перехода.

Топология кристалла была разработана с учётом конструктивно-технологических ограничений и требований. Размеры диффузионных резисторов, использованных в схеме, были рассчитаны упрощённым методом.

Разработанная топология интегральной микросхемы не требует сложного оборудования и обеспечивает приемлемый результат для заданной схемы.

Список используемой литературы.

1. Николаев И.М., Филинюк Н.А. Интегральные микросхемы и основы их проектирования. - М.: Радио и связь. 1992 .

2. Конструирование и технология микросхем. Курсовое проектирование под ред. Коледова Л.А. - М: высшая школа. 1984

3. Степаненко И.П. Основы микроэлектроники - М.: Советское радио, 1980

4. Черчение под ред. Куликова А.С. - М: высшая школа, 1989

5. Малышева И. А. Технология производства интегральных микросхем - М: Радио и связь, 1991 .