Специализированные модели управления (СМУ) систем технического зрения

СОДЕРЖАНИЕ: Исходные данные, общая структура и основные этапы проектирования системы технического зрения. Рассмотрение функций и его реализация на базе однокристального микропроцессора КР1810. Разработка аппаратных средств и расчет времени работы программы.Специализированные модели управления (СМУ) систем технического зрения

1. Исходные данные для проектирования

Необходимо построить СМУ, которое определяет положение движущегося объекта в поле зрения робота на каждом кадре изображения. Изображение, полученное с датчика, преобразуется в цифровую форму и представляется в виде матрицы размерностью М х N точек (M = N = 128). Каждая точка представляет собой яркость, которая закодирована 8 разрядами.

Размеры объекта mх n точек (m = n = 16). Положение объекта определяется путём нахождения координат точки, в которой принимает минимальное значение корреляционная функция Rисходного и эталонного изображения. Минимум функции Rищется на каждом кадре в поле Uразмерностью r х p (r = p = 5). Корреляционная функция для точки с координатами l, k в поле U вычисляется по формуле:

![]() ,

,

где ![]() точки исходного изображения;

точки исходного изображения; ![]() точки изображения эталона.

точки изображения эталона.

Начальное положение центра области U:

Хцн = М/2; Уцн = N/2.

Частота смены кадров 50 Гц.

Координаты объекта должны быть определены за время существования одного кадра.

2. Этап системного проектирования

На этом этапе необходимо разработать общий алгоритм функционирования системы технического зрения и её структурную схему.

Исходя из задания на проектирование системы технического зрения (СТЗ) должна выполнять следующие функции:

-преобразование аналогового сигнала, поступающего с датчика (Д) в цифровую форму;

-запоминание цифровых значений яркости точек в памяти;

-чтение цифровых значений яркостей точек в памяти;

-чтение цифровых значений яркостей точек исходного и эталонного изображений и вычисление функций корреляции;

-нахождение минимального значения функции корреляции в области U и выдача новых координат области V.

Преобразование аналогового сигнала и запись полученного цифрового значения должен осуществлять блок аналого-цифрового преобразователя (АЦП).

Для запоминания полученных цифровых значений яркостей точек необходимо оперативное запоминающее устройство изображения (ОЗУИ). Объём его определяется максимальными размерами представления изображения, то есть (M х N) 8 разрядных ячеек.

Требуемый объём ОЗУИ равен 16 Кбайт.

Для хранения эталона необходимо иметь постоянное ЗУ объёмом m х n байт (ПЗУ), т.е. 256 байта.

Чтение данных из ОЗУИ и ПЗУ, вычисление функций корреляции, нахождение минимального значения R и определение новых координат области U должно производиться вычислительным устройством (ВУ).

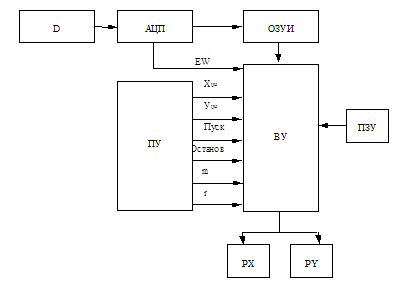

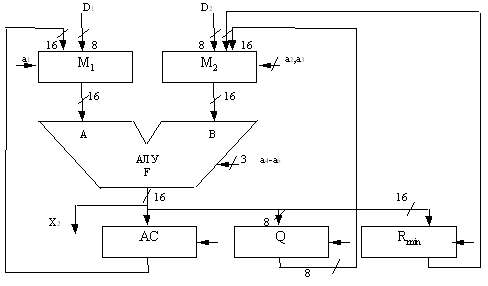

Для хранения новых координат необходимы два регистра РХ и РY. Запуск и останов ВУ производиться с пульта управления (ПУ). На рис. показана общая структура СТЗ.

Блок АЦП синхронно с частотой дискретизации осуществляет запись информации в ОЗУИ. По окончании записи одного кадра он выдаёт сигнал конца записи EW. ВУ опрашивает сигнал EWи, получив его, переходит на следующем кадре к вычислению функций корреляции и нахождению их минимума. Затем ВУ записывает в регистры PX и PYзначения найденных координат и переходит к опросу сигнала EW.

Рисунок 1 Общая структура СТЗ

Таким образом, доступ к ОЗУИ имеют поочерёдно блок АЦП (по записи) и ВУ (по чтению).

3. Проектирование отдельных блоков СТЗ

Организация блоков АЦП, ОЗУИ, ПЗУ трудности не представляет. Они выполняются по стандартным решениям. Остановимся на проектировании ВУ. Оно должно на каждом кадре осуществлять формирование координат точек области U, вычисление функций корреляции R в каждой из этих точек, для чего необходимо вычислять адреса точек исходного и эталонного изображений, находить минимальные значения функции корреляции и координат точки.

Внешний интерфейс ВУ:

D1 информационная шина с ОЗУИ;

D2 информационная шина с ПЗУ;

Пуск, Ост линии для передачи сигналов Пуск и Останов с ПУ; EW линия передачи сигнала EWс блока AЦП; Хцн , Yцн шины ввода начальных координат; A1 шина адреса на ОЗУИ; A2 шина адреса на ПЗУ; X,Y шины координат X и Y.

Определим внутренние запоминающие элементы: регистры Xц , Yц и Xт , Yт для хранения координат соответственно центра и точек области U; X’т Y’т для хранения текущих координат точек окна вычисления функции R; AC для формирования текущего значения функции R; Rmin регистр минимального значения функции корреляции; m, n для хранения размеров окна; r, p для хранения размеров области U; Q рабочий регистр; счётчики k, l для организации циклов сканирования области U; i, j для организации циклов сканирования окна вычисления функции R.

Так как m = n и r = p, то необходимо иметь только по одному регистру (m и r).

Определим разрядность регистров.

Все регистры координат имеют одну разрядность, определяемую как ![]() . В данном случае разрядность должна быть равна 7. Так как организация микросхем такова, что разрядность кратна 2, выбираем разрядность регистров Xц

, Yц

, Xт

, Yт

, X’т

, Y’т

равной 8.

. В данном случае разрядность должна быть равна 7. Так как организация микросхем такова, что разрядность кратна 2, выбираем разрядность регистров Xц

, Yц

, Xт

, Yт

, X’т

, Y’т

равной 8.

Разрядность АС, Rmin

определяется максимально возможным значением функции корреляции. Максимальное значение получается, если яркости всех точек в окне исходного изображения максимальны (![]() - 1), а яркости всех точек эталонов - минимальны (0).

- 1), а яркости всех точек эталонов - минимальны (0).

В этом случае максимальное значение равно ![]() .

.

Следовательно, необходимо иметь 14 разрядов. Принимаем разрядность регистров АС и Rmin равной 1 Разрядность регистра Q может быть равна 8.

Количество разрядов регистров m, r и счётчиков k, l и i, j равно соответственно ![]() и

и ![]() , т. е. четырём и трём.

, т. е. четырём и трём.

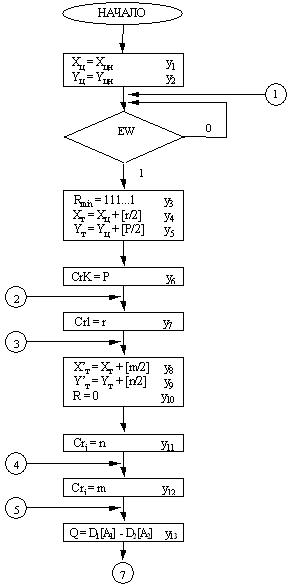

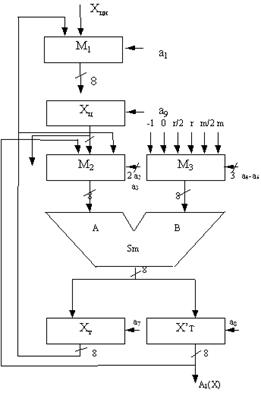

Шина A1 формируется из выходов регистров X’т и Y’т , а шина A2 из i и j. Алгоритм функционирования ВУ показан на рис. 2.

В зависимости от требований к аппаратурным затратам и быстродействию данный алгоритм может быть реализован различными способами. По аппаратурным затратам самой экономичной является реализация, при которой все операции над регистрами выполняются на одном блоке обработки.

Однако при этом все операции выполняются последовательно и значит, быстродействие самое низкое.

Самой быстродействующей является реализация, при которой все возможные для совмещения операции выполняются на своих блоках обработки.

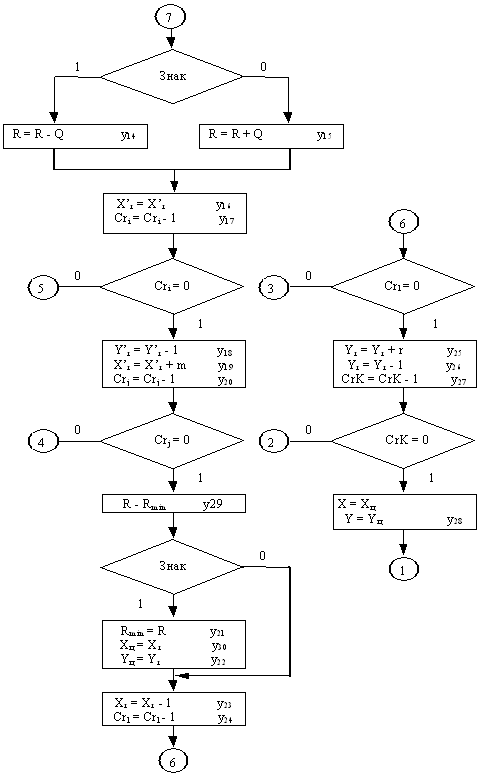

Исходя из алгоритма, можно выделить следующие параллельно работающие блоки:

-арифметический (АР);

-формирование координаты Х адреса (АХ);

-формирование координаты Y адреса (AY);

-счётчиков (СК);

-управления (БУ).

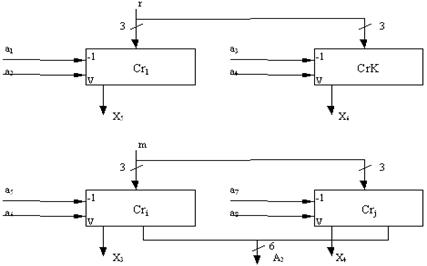

Блоки АР, АХ, AY, СК образуют операционный блок. Структурная схема для такого разделения изображена на рис. 3.

Арифметический блок выполняет микрокоманды Y3 , Y10 , Y14 , Y15 , Y29 , Y21 .

Блок формирования координаты АХ выполняют микрокоманды Y1 , Y4 , Y8 , Y16 , Y19 , Y30 ,Y23 , Y25 .

Блок формирования координаты AY аналогичен блоку АХ и служит для выполнения микрокоманд Y2 , Y5 , Y9 , Y18 , Y22 , Y2

Блок счётчиков служит для организации циклов и выполняет микрокоманды Y6 , Y7 , Y11 , Y12 , Y17 , Y20 , Y24 , Y27 .

Блок управления предназначен для формирования управляющих сигналов аi , подаваемых на все блоки, для организации условных и безусловных переходов. Условные переходы производятся по сигналам: внешних условий (Х1 ), арифметического блока (Х2 ), с блока счётчиков (Х3 - Х6 ).

Рисунок 2 Алгоритм функционирования ВУ

Рисунок 2 Окончание рисунка

Рисунок 3 Структурная схема оптимальной реализации

На рис. 4. показан пример организации арифметического блока (М1 и М2 мультиплексоры; АЛУ арифметико-логическое устройство; ai управляющие сигналы).

Рисунок 4 Организация арифметического блока

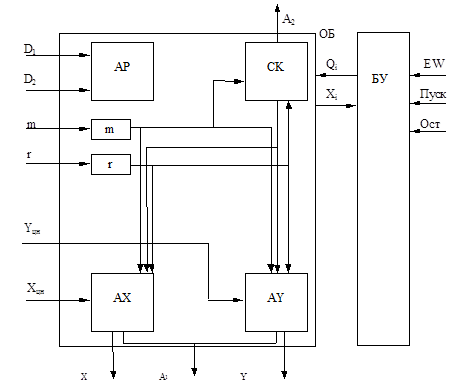

Блок управления может выдавать на каждый из блоков код микрокоманды, который с помощью дешифратора переводится в набор управляющих сигналов ai . Организация блока AX(AY) показана на рис. 5, а схема блока счётчиков на рис. Определим теперь для такой реализации время выполнения алгоритма, показанного на рис.2.

Т = [(((4m+3)n+6)r+3)p+4] tц ,

где tц - время одного цикла.

Время цикла определяется временем прохождения сигналов по самому длинному пути среди всех блоков. В рассматриваемом устройстве таким путём является: чтение данных из ОЗУИ и ПЗУ, прохождение через мультиплексоры М1 и М2 арифметического блока, выполнение операции на АЛУ и запись в регистр Q.

Рисунок 5 Организация блока формирования координаты

В этом случае время цикла:

tц = tчт + tм + tАЛУ + tQ .

При построении устройства на элементах ТТЛШ логики может быть порядка 200 нс.

Если ввести конвейерные регистры на выходах ОЗУИ и ПЗУ, то время цикла можно уменьшить в два раза.

Для tц = 200 нс; Т = 5,4 мс.

Рисунок 6 Организация блока счётчиков

4. Реализация СТЗ на базе однокристального микропроцессора (КР1810)

технический зрения микропроцессор аппаратный

Рассмотрим пример реализации СТЗ при использовании в качестве ВУ микропроцессора КР1810 ВМ8 При разработке будем использовать общий алгоритм рис.2.

Разработка структуры аппаратных средств

Для разработки структуры ВУ на базе МП КР1810 ВМ86 необходимо поставить в соответствие элементы и узлы рис.3 - 6 элементам и узлам МПК.

Один из вариантов такого соответствия приведён в табл.

Таблица 1 Варианты соответствия

| Переменные | Запоминающие узлы |

| Хцн , Yцн | 16-разрядный регистр PXYЦ(входной порт) |

| M(n) | 8-разрядный регистр РМ(вх. порт) |

| r(p) | 8-разрядный регистр PR(вх. порт) |

| X,Y | 16-разрядный регистр РXY(выходной порт) |

| Xт ,Yт | 16-разрядной РОН ВР |

| Rmin | 16-разрядные ячейки стека |

| Xц , Yц | 16-разрядные ячейки стека |

| K | 8-разрядный РОН CH |

| L | 8-разрядный РОН CL |

| J | 8-разрядный РОН BH |

| I | 8-разрядный РОН BL |

| A1 (X’т ,Y’т ) | 16-разрядный РОН SI |

| А2 | 16-разрядный РОН DI |

| R | 16-разрядный РОН DX |

| Q | 16-разрядный РОН AX |

| EW | 1-разрядный регистр PEW (входной порт) |

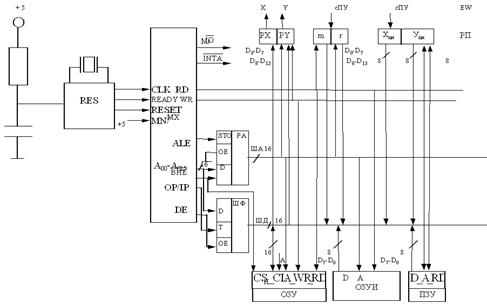

Входные и выходные порты (регистры PXYЦ, РМ, PR, PXY, PEW) программно доступны МП как устройства ввода - вывода. Адреса регистров приведены в табл.2.

Таблица 2 Распределение адресов

| Регистр | Условное обозначение адреса |

Адрес |

| PXYЦ | Port Xц | 00Н |

| P | Port m | 02Н |

| PR | Port r | 03Н |

| PXY | Port X | 04Н |

| PEW | Port EW | 06Н |

Регистры могут быть выполнены на микросхемах КР580ИР82(83) или КР 580ИК55. Память изображения и эталонов является программно доступной со стороны процессора как память данных. Распределение главной памяти приведено в табл. 3.

Таблица 3 Распределение памяти

| ОЗУИ | 0000-3FFF |

| ПЗУ | 4000-40FF |

| СТЕК | 5000-50FF |

| Память программ | 6000-FFFF |

Координаты X и Y хранятся не в отдельных регистрах, а в одном 16 - ти разрядном регистре (ячейке памяти). Для адресации памяти достаточно 16 разрядов адреса. Регистры сегментов, кроме CS, перегружать после начальной установки не нужно. Адреса, выдаваемые по мультиплексированной шине адреса данных, запоминаются буферными регистрами К580 ИР82. Нагрузочная способность шины данных повышается шинными формирователями К580 ВА8 В рассматриваемом примере достаточно организовать работу МП в минимальном режиме. Структура ВУ на МП показана на рисунке 7.

Рисунок 7 Структура вычислительного устройства на МП4.2

Разработка программы функционирования

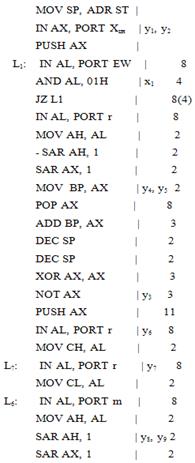

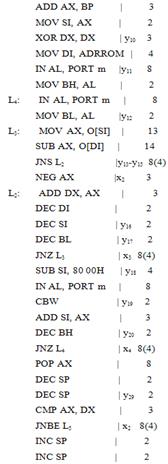

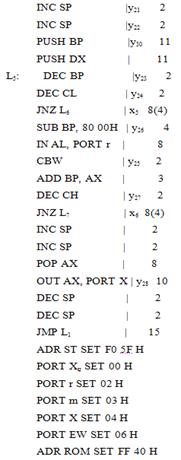

Программа разработана в соответствии с алгоритмом, показанным на рис. 2. На рис. 8 приведён текст программы на языке ассемблера и соответствие микрокоманд алгоритма.

Рисунок 8 Программа функционирования

Расчёт времени работы программы

Зная время выполнения каждой команды (см. рис. 8), можно определить общее время выполнения программы:

Т = [(((52m + 37)n + 97)r + 37)p+74]tц ,

где tц определяется тактовой частотой процессора, tц = 200 нс.

Для m = n = 16 и r = p = 5; T = 70 мс.